本篇目录:

能延迟导通的元器件

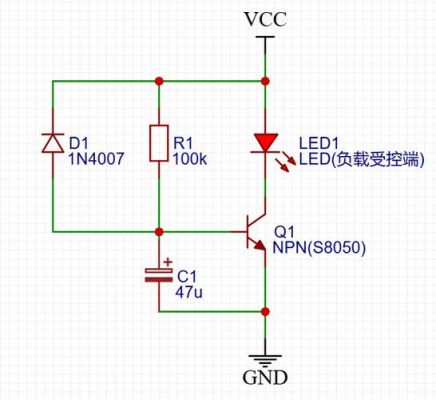

电容器(Capacitor):电容器是存储电荷的元件,可以在电路中产生延时效果。在RC电路中,通过在电容器和电阻之间连接电源,电容器会逐渐充电或放电,从而产生延时效果。电感器(Inductor):电感器是存储磁能的元件,可以在电路中产生延时效果。

可以利用mos做延时导通,在mos Vgs之间使用RC放电,使mos缓慢开启就可以实现了。

可使用肖特基二极管,例如1N5817,正向电流小于0.5A时,正向压降可低至0.2V以下。

数电经典面试题88问(二)

1、以下是数电经典面试题88问(二)的具体内容,包含多个段落和使用p标签标记。正逻辑与负逻辑的区别在于,若用1表示高电平,0表示低电平,则为正逻辑;反之,为负逻辑。TTL电路以三极管BJT和电阻为基础实现逻辑电路,其最大优点是响应速度快,通常传输延时在5~10ns。

2、频率特性好、体积小、功耗小,便于电路的集成化产品的袖珍化,此外咋i兼顾抗震可靠等方面也特别突出,但在失真度和稳定性方面不及真空器件。

3、不知道你的模电数电学到那种程度,不过这是门实践性很强的科目,只有真正接触或做出产品才能有更深刻的了解,现正从事这方面的工作,个人感觉想要快速成长基础、概念最重要。面试时问的都是些比较实际的问题(关于他们的产品),而当你进入他们那个圈子,就会发现那些其实是很简单的问题,远比不上你以前学到的那些深奥难懂。

4、、给出多个mos管组成的电路求5个点的电压。(Infineon笔试试题)2电压源、电流源是集成电路中经常用到的模块,请画出你知道的线路结构,简单描述其优缺点。(仕兰微电子)2画电流偏置的产生电路,并解释。(凹凸)2史密斯特电路,求回差电压。

5、我是电气工程及其自动化的,和你差不多。基本的问题网上有很多,但我觉得我们面试强电的时候一般会问你CAD掌握的怎么样?供配电各个规范有无了解?会不会看图,作图?等等。

6、没有,机电专业的学生 对单片机 和 C ,数电,模电 都理解不了,就算知道点的,也就皮毛。你也无法培养。应该招电子工程专业。

网络中delay和latency的区别

1、概念区别:latency:等待;潜伏期;延迟。主要指时钟延迟,具体指的是输入数据与输出结果(该数据经过一系列处理之后的结果)之间的延时。delay:延迟;延误。主要指器件延时、布线延时,是时序器件之间的逻辑延时。

2、总结来说,delay关注的是信号在电路中的流动速度,而latency则侧重于数据处理和通信的响应时间。在设计和优化网络性能时,理解并准确区分这两个概念至关重要。

3、网络中,delay和latency都表示数据传输过程中的延迟,但它们的含义和应用场景有所不同。Delay与Latency的基本含义 在网络通信领域,Delay和Latency是两个描述数据传输过程中时间延迟的术语。尽管它们在某种程度上可以互换使用,但它们的应用背景和含义确实存在差异。

4、首先请注意,同一个词在不同领域,可能出现歧义。通信方面,它们的区别来自英文。其中latency只能用作名词,delay可以用作名词、动词。

5、带宽(Bandwidth):带宽是指网络传输数据的能力,通常以每秒传输的比特数(bps)来表示。带宽越高,网络传输速度越快。 时延(Latency):时延是数据从发送端到接收端所需的时间。

6、时延(delay或latency):数据(一个报文或分组,甚至比特)从网络(或链路)的一段传送到另一端的时间。也称延迟。发送时延:主机或路由器发送数据帧所需的时间,也就是从发送数据帧的第一个比特算起,到该帧的最后一个比特发送完毕所需的时间。也成传输时延。

FPGA与CPLD的区别在哪?

1、CPLD与FPGA的主要区别在于其结构、编程方式、应用特点以及成本等方面。基本结构 CPLD是一种复杂的可编程逻辑器件,主要由多个逻辑单元组成,如可编程阵列逻辑、通用阵列逻辑等。它预先定义了固定的硬件结构,开发者通过编程实现特定的功能。

2、逻辑结构不同:CPLD类似PAL、GAL,拥有丰富的组合逻辑电路资源。FPGA:类似门阵列,拥有丰富的触发器、存储器资源;CPU、DSP等IP核。集成度不同:CPLD:500~50000门;CPLD:500~50000门;FPGA:1K~10M门。互连结构不同:CPLD:等长度的互连线资源,其特点是延时相等。

3、cpld和fpga的区别如下:CPLD更适合完成各种算法和组合逻辑,FPGA更适合于完成时序逻辑。CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。在编程上FPGA比CPLD具有更大的灵活性。FPGA可在逻辑门下编程,而CPLD是在逻辑块下编程。

4、cpld与fpga的区别有: 结构差异。CPLD基本上采用乘方结构的互联结构;而FPGA采用一种小单元的阵列排列结构。这种结构上的差异导致了两者在设计和应用上的不同。 编程方式差异。

5、FPGA与CPLD区别 ①CPLD更适合完成各种算法和组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构。②CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。

6、CPLD与FPGA在结构方面的区别:CPLD是粗粒结构,这意味著进出器件的路径经过较少的开关,相应地延迟也小。因此,与等效的FPGA相比,CPLD可工作在更高的频率,具有更好的性能。CPLD的另一个好处是其软件编译快,因为其易于路由的结构使得布放设计任务更加容易执行。

逻辑电路的延迟时间

此延时是由PN结电容及电路内器件的响应时间及线路长度共同决定的。在器件的使用手册中有详细的上升沿下降沿及响应时间。如果是频率很高的高速电路中,电路板的导体长度也有影响,毕竟电波再快也有速度。

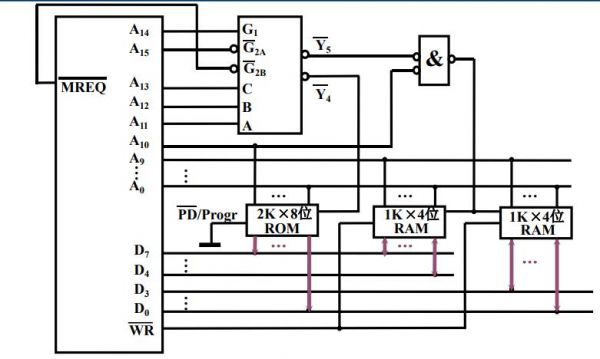

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。 用D触发器,格雷码计数器,同步电路等优秀的设计方案可以消除。

封锁脉冲是在输入信号发生竞争的时间内,引入一个脉冲将可能产生尖峰干扰脉冲的门封锁住,从而消除竞争冒险。封锁脉冲应在输入信号转换前到来,转换结束后消失。 加选通脉冲消除竞争冒险 选通脉冲是当电路输出端达到新的稳定状态之后,引人选通脉冲,从而使输出信号是正确的逻辑信号而不包含干扰脉冲。

到此,以上就是小编对于逻辑图中怎么表示延时的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏