本篇目录:

- 1、DSP通过EMIF总线,接收FPGA发来的16位数据,处理后再发回给FPGA,该怎样实...

- 2、FPGA双向IO口和IIC协议

- 3、FPGA纯verilog实现UDP协议栈,sgmii接口SFP光口收发,提供工程源码和技术...

- 4、FPGA和USB3.0通信-USB3.0协议介绍

- 5、基于FPGA的千兆以太网数传系统设计

- 6、[FPGA/VerilogHDL/Xilinx]SerDes接口设计

DSP通过EMIF总线,接收FPGA发来的16位数据,处理后再发回给FPGA,该怎样实...

1、初始化DSP:在DSP上电或复位后,初始化EMIF接口和相关寄存器。设置中断服务程序(如果使用中断方式接收数据)。接收FPGA数据:配置FPGA以将数据发送到DSP的EMIF接口。在DSP上,配置一个接收缓冲区来存储从FPGA接收的数据。使用轮询或中断方式检查是否有数据到达。如果有,从EMIF接口读取数据并存储到缓冲区。

2、ZYNQ的PL端例程存放在资料盘Demo\ZYNQ\PL\FPGA_DSP_EMIF文件夹内,而DSP的例程则在Demo\DSP\XQ_EMIF16中等待启动。2 功能呈现 关键的EMIF16接口在ZYNQ与DSP之间架起了一座桥梁,使得数据能在4096字节的容量内双向传输。首先,DSP通过EMIF16接口发送数据,ZYNQ接收到后进行存储,同时作为读取源。

3、这三个引脚可以用来连接异步存储器、SDRAM存储器、SBSRAM存储器,进行一些功能控制。因此引脚电平高低应该要根据你连的是什么类型的存储器来决定的。TMS320C6000 DSP EMIF Reference Guide文档里提到了这些引脚的高低电平。DSP的CE0-CE3是通过CE[0:3]空间片选引脚的高低电平来进行区分的。

FPGA双向IO口和IIC协议

1、不行的,建议你在Fpga中分两个模块,分别为主从接口,分别与外部主从机相连接,内部做数据的处理和交换。你可以把需求说清楚些,我给你出个方案。

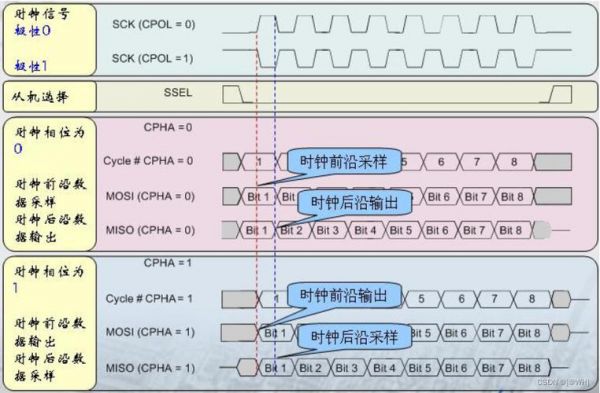

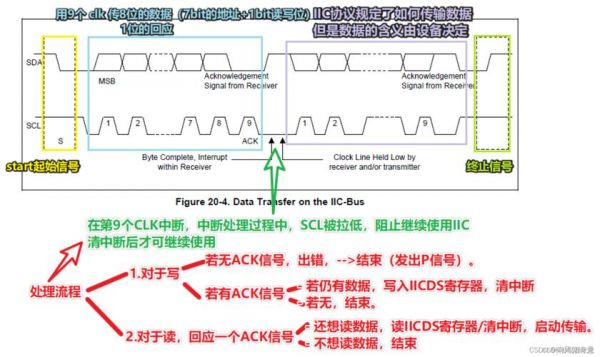

2、mcu有IIC接口和SPI接口,SPI速度较快,但是比IIC多用一条线。如果用IO口模拟IIC或SPI,要注意有的MCU的IO不能支持双向数据传输,这样只能用SPI。另外二者传输距离都不能太长,多见于板内通信。

3、先看你是做什么用?有没有通讯协议?一个单片机和多个74LS373进行片选可以扩展I、O口,74LS373是双向的。另外还有74LS245也是双向的,可以扩展单片机IO,不过如果你要用扩展IIC、或者串口、单总线,尽量直接接到单片机引脚。

FPGA纯verilog实现UDP协议栈,sgmii接口SFP光口收发,提供工程源码和技术...

FPGA纯verilog实现的UDP协议栈和sgmii接口SFP光口收发功能,为用户提供工程源码和技术支持,旨在解决现有UDP解决方案的不足。市面上的UDP实现方案存在缺陷,如一些仅实现基础功能而缺乏ping功能,或者虽有ping但不开源,难以排查问题。另一些方案虽功能全面,但依赖于需要许可证的IP核或不提供源码。

本设计采用纯verilog实现的25G-UDP高速协议栈,专注于提供25G-UDP回环通信测试。它旨在为用户提供一个高度可移植、功能丰富的25G-UDP协议栈架构,支持用户根据需求创建自己的项目。该协议栈基于主流FPGA器件,提供了一系列工程源码,适用于Xilinx系列FPGA,使用Vivado作为开发工具。

FPGA 高端项目:基于 SGMII 接口的 UDP 协议栈,提供2套工程源码和技术支持 前言:在实现 UDP 协议栈的过程中,网上有许多可用的资源,但大多存在一些局限性,如功能不全面、缺乏源码或难以进行问题排查。

FPGA和USB3.0通信-USB3.0协议介绍

首先,我们需要理解几个基本概念。USB0由总线、接口和协议三大组成部分构成。总线是一组传输通道,为逻辑器件之间的数据传输提供途径。接口则是物理连接标准,用于设备间的物理连接。协议则定义了数据传输的规则,为所有成员提供协作框架,以确保信号能够顺利传输。USB协议的复杂性源于不同的概念解释差异。

USB工业相机具有易用性、稳定性、低成本等优点, 具有一个可进行完全配置的并行通用可编程接口GPIF II,最大位宽32位,频率100MHZ,它可与任何处理器、ASIC 或 FPGA 连接。想选择一款合适的USB工业相机,不如选Regem Marr 研祥金码,内置丰富的IO接口,支持复杂现场需求。

本身带有高速CPU,没有其他必要的话尽量省去其他控制芯片 芯片的USB接口一般只提供传输层的接口,协议层的东西一般是自己写的,C公司的芯片没做过,不过你可以参考C公司的网站教程。

另一方面,由于EZ-USB FX3 内部有比EZ-USB FX2LP更多的RAM,加上传输带宽也高了非常多,这就使得用最简硬件结构(不使用FPGA和外部存储芯片等)开发的USB工业相机也可以有很好的稳定性和很高的实际帧率。

存储:建议选择至少256GB的固态硬盘(SSD),以提高系统运行速度和软件加载速度。 显卡:集成显卡通常足够应对学习和模拟电路。若需要进行图像处理或游戏等需求,可选择独立显卡,如NVIDIA GeForce系列。 屏幕:13英寸或15英寸的高分辨率显示屏能够提供更好的工作体验。

看具体应用,像pcie usb0、sata之类的,还是倾向于买原厂。

基于FPGA的千兆以太网数传系统设计

1、写了用以太网传输的优点,相对于串口的传输速度慢,并且不能远距离传输。PCIE不能远距离传输,选择以太网兼顾了传输速率和系统使用灵活的特点。选择的Xilinx公司的xc7vx485T的FPGA开发板VC707的优点 集成了MAC硬核和SGMII接口,可以完成MAC层功能和PHY层接口的实现。

[FPGA/VerilogHDL/Xilinx]SerDes接口设计

在Xilinx FPGA中,SerDes接口扮演着至关重要的角色,它带来了串行高速数据传输技术的革新。该接口配备了MGT收发器,这种收发器不仅支持高速转换、时钟恢复和编码/解码功能,还能符合Serial RapidIO、FC、PCIe等多种工业标准,使得数据传输速度能够轻松超过10Gb/s。

Xilinx 公司开发的 SerDes 收发器 IP 核 Rocket IOTM,也被广泛地用于其高端FPGA中,为广大用户提供了兼容XAUI,PCI Express,Serial RapidIO 等规范的 FPGA 解决方案,获得了市场的良好反响。SerDes硬核作为高端FPGA的冲击市场的有力武器,而对于低端FPGA来说,软的SerDes不失为一种非常好的研究方向。

吉比特SERDES的物理实现通常采用基于差分的电接口形式,常见的差分信号形式有CML、LVDS等。CML是最常见的接口类型,适合吉比特链路,具有可选的交流或直流终端和输出驱动,以及可选的内置线路均衡和/或内部端接。LVDS也是常用的接口类型,在Xilinx的管脚约束中经常被用作差分引脚的电平选择。

将BIT文件下载到FPGA后,使用ChipScope Analyzer连接到FPGA上,就会出现IBERT的GUI调试界面。a) 检查PLL是否LOCK,如果没有,需要检查时钟和电源。比如时钟频率是否正确,SERDES是否选择了正确的时钟源。b) 将SERDES的TX和RX设为相同的数据pattern,例如PRBS-31。设置SERDES为Near-end PMA模式。

放在近端比较好一些,对于Serdes信号来说,加AC耦合电容主要是考虑近端和远端串扰,按照串扰的原理,对于理想的带状线(strip-line)来说,近端串扰相互加强,远端串扰相互抵消,因此AC耦合电容加在靠近发送端会更有效。

到此,以上就是小编对于fpga通讯的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏