本篇目录:

- 1、亚稳态及跨时钟域的处理办法

- 2、FPGA设计中跨时钟域常见的问题(读书笔记)

- 3、基于FPGA的千兆以太网数传系统设计

- 4、vivado怎么让跨时钟域

- 5、fpga与dsp通讯怎样同步时钟频率

- 6、pcb设计中FPGA与高速并行DAC的布线应该注意什么?

亚稳态及跨时钟域的处理办法

不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。

可以理解为因为有跨时域的设计,在设计中容易出现亚稳态现象,所以要做好跨时钟域同步。然后重点看这几种方案。

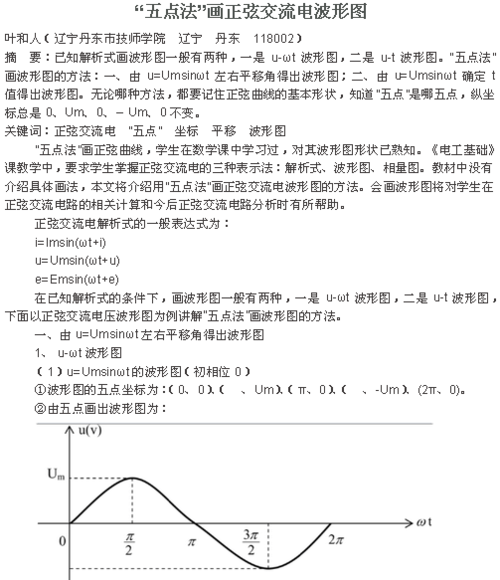

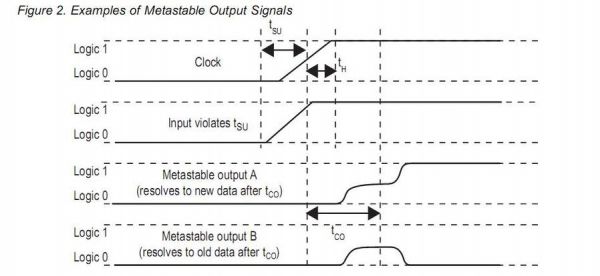

在同一时钟域中,可以采用时序约束来满足建立时间(Tsu)和保持时间(Th)。对于异步信号,在输出稳定前可能会出现毛刺、振荡、不固定的电压值,还会有亚稳态的传播。

) 采用两级D触发器缓存,把“xreq”信号同步到接收器的时钟域“yclk”上,得到“yreq2”信号,当采样到yreq2有效后,将数据锁存到系统y的总线上,同时接收器发出“yack”信号(相应信号)。

FPGA设计中跨时钟域常见的问题(读书笔记)

从摘要中可以了解到这篇文章主要写了(1)亚稳态现象的出现(2)四种跨时钟域同步方案(3)评估分析(4)优化设计 可以理解为因为有跨时域的设计,在设计中容易出现亚稳态现象,所以要做好跨时钟域同步。

亚稳态常见于异步电路。异步复位电路是常见例子,由于复位信号与时钟信号不同步,所以无法保证复位信号的移除时间和恢复时间满足要求,可能导致复位失败。跨时钟域数据传输时,由于两个时钟域信号变化不同步,也可能产生亚稳态。

通常情况下,同一个时钟下的时钟歪斜不应该超过300ps,同步跨时钟域路径的时钟歪斜不应该超过500ps,异步跨时钟域路径的时钟歪斜一般比较大,因为它们的时钟源不同。

基于FPGA的千兆以太网数传系统设计

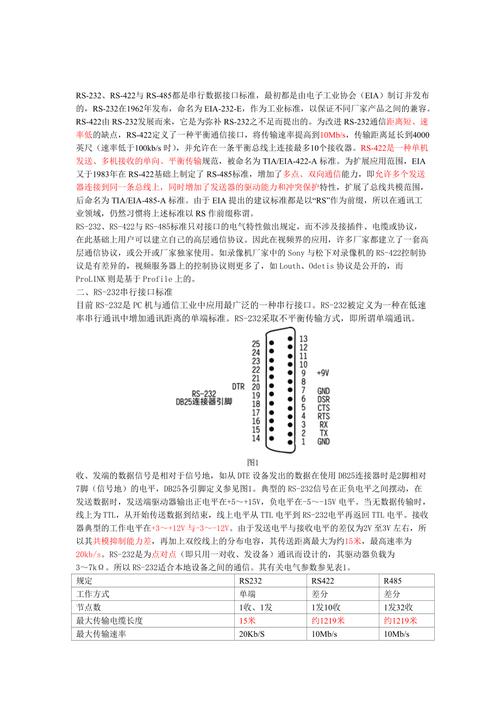

写了用以太网传输的优点,相对于串口的传输速度慢,并且不能远距离传输。PCIE不能远距离传输,选择以太网兼顾了传输速率和系统使用灵活的特点。

以FPGA方式实现千兆以太网设计,有效提高了系统的可靠性和集成度,能够满足未来较长时间国内星载计算机系统在千兆以太网方面的实际应用需求。简介:88E1111是一款经典的三速以太网PHY芯片,可工作在10/100/1000Mbps下。

百兆以太网应用场景广,适用于突发通信和继续传送大型数据文件,互换操作性好,具有广泛的软硬件支持。

一般的ip核都有自动生成工具,比如Altera有megacore wizard,按照你需要的功能enable或者disable选项就可以了。具体步骤可以上Altera或者Xilinx的网站,搜索你需要的以太网ip核关键字,比如GE或者FE,以及是否需要MAC,PCS功能等。

您甚至可能希望随时重新配置FPGA,改变外设。 开发基于FPGA的外设系统相对简单,FPGA供应商提供IP库以及基于GUI的设计工具,使您很容易连接外设IP和硬核处理器。对此,设计流程与使用Nios II处理器等软核CPU的流程完全相同。

在CPCI系统环境下高速数字通信AFDX协议端系统接口的电路设计与功能实现。采用Verilog编程实现基于FPGA的硬件设计部分,采用C编程实现基于MicroBlaze的嵌入式软件设计。 0 引言 随着通信技术的高速发展,嵌入式系统对数据传输速率的要求更高。

vivado怎么让跨时钟域

BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。当S为低电平时输出时钟为I0,反之为I1。需要指出的是BUFGMUX的应用十分灵活,I0和 I1两个输入时钟甚至可以为异步关系。

如果两个时钟之间没有路径,在两个时钟之间可以简单的使用set_clock_groups 或者set_false_path约束 如果跨时钟域路径都是一位的,那么你可以在两个时钟之间使用set_clock_groups 或者 set_false_path。

在Set Up Debug中,工具会自动分析信号的所在时钟域,并添加时钟。少数情况,可以通过右键点击Select Clock Domain来修改时钟域。

fpga与dsp通讯怎样同步时钟频率

1、找一款简单的dsp芯片,比如ti的54系列,看看emif接口,fpga可以跟emif挂接,然后用emif的读写来操作fpga内部逻辑。不过,fpga的逻辑时序要符合dsp的emif接口时序。先把dsp看好。

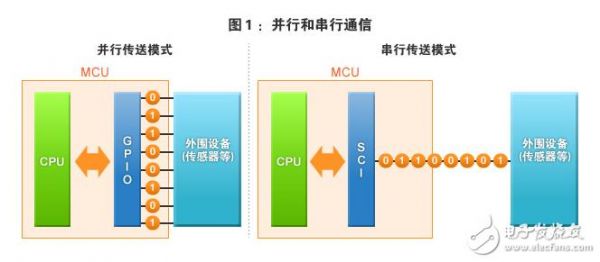

2、在同一块板子上可以使用EMIF,DMA,PPI传输,速度慢一点的可以IIC,SPI,如果不在一块板子上,速度慢可以RS485,速度快得可以使用LVDS传输。

3、①同步时钟(synchronous clock) 两个时钟之间的相对相位关系是固定的(两个时钟来源于同一个Primary clock),并且这两个时钟的频率的最小公共周期是个整数。

4、在相同频率下,任何CPU对外界信号的响应都没有FPGA快!因为CPU对外界的响应,尤其是中断,需要几个机器周期,中断下甚至还得进行压栈过程!而FPGA就没有这些琐事了,其运行完全按照同步时钟来的。

pcb设计中FPGA与高速并行DAC的布线应该注意什么?

PCB元件封装库要求较高,它直接影响PCB的安装;原理图SCH元件库要求相对宽松,但要注意定义好管脚属性和与PCB元件封装库的对应关系。

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。

电路设计要注意的十四个误区 误区一:这板子的PCB 设计要求不高,就用细一点的线,自动布吧。

高速信号PCB布线应注意什么?电源滤波一定要做好,否则有纹波。正电源(VCC)的所有线路最好用两根地线(GND)将它夹在中间,(如果整个板子都铺铜,这个可以不考虑)。

到此,以上就是小编对于fpga 时钟域的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏