本篇目录:

- 1、如何解析vivadoxdma(pcie)核数据传输原理(双口ram)?

- 2、(PCIE学习应用教程)2.AXI4-Lite协议简明学习笔记

- 3、axi4-stream和pcie怎么直接进行数据传输?

- 4、如何解析vivadoxDMA(PCIe)核数据传输原理(双口ram)?

- 5、XDMA学习笔记:EP模式

如何解析vivadoxdma(pcie)核数据传输原理(双口ram)?

视频输入通过笔记本模拟的HDMI接口,解码和缓存由silicon9134和AXI4总线完成,其中还包含3帧缓存,保证了数据的稳定传输。Vivado工程详解 针对Xilinx的xc7k325tffg900-2开发板,我们使用Vivado 2011进行设计,输入为HDMI,输出为PCIe X8,目标是实现QT上位机的显示试验。

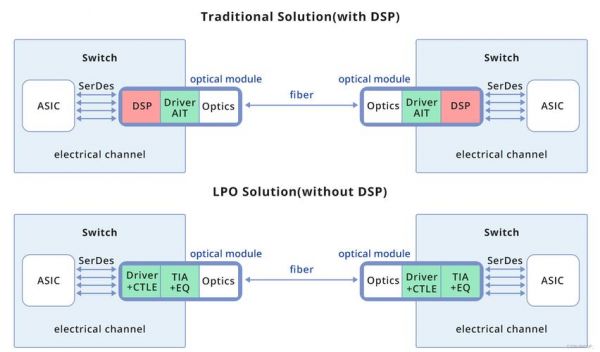

PCIE的实现通常依赖于XDMA,这是一种由Xilinx提供的高性能、可配置的DMA解决方案,适用于PCI Express 0与0的SG模式,并支持AX 4接口或AX-Stream接口。在SG模式下,主机通过构建链表来组织待传输数据,并通过BAR(Base Address Register)将链表首地址传递给XDMA。

在Vivado项目中,通过IP Catalog搜索并添加XDMA IP核到设计中。配置XDMA IP:Basic配置:选择DMA模式。设置基本模式、设备/端口类型。配置PCIe块位置、通道宽度、最大链路速度等参数。设置AXI地址宽度、AXI数据宽度、AXI时钟频率。选择DMA接口选项和AXI4Lite从接口。PCIe ID配置:通常保持默认设置,无需更改。

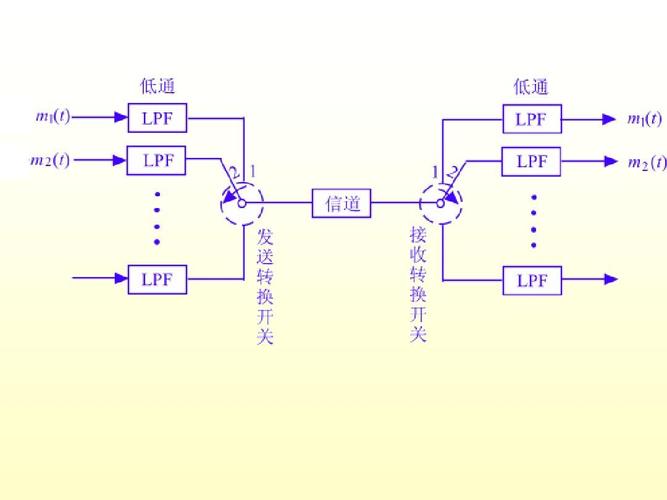

理论知识:XDMA传输流程图 H2C通道:在vivado配置中设定数量,负责主机到卡的DMA传输。它会根据最大读取请求大小和内部资源拆分请求,保留未完成请求,直到写入完成。读取和写入事务在数据FIFO空间内拆分,PCIe RC块会将完成数据返回给已分配的缓冲器,同时开始向用户接口发出写入请求。

(PCIE学习应用教程)2.AXI4-Lite协议简明学习笔记

1、通过勾选PCIe to AXI Lite Master Interface,设置默认1MB的空间大小,上位机与FPGA之间即可实现通过PCI-E进行读写寄存器的操作。选择AXI4-Lite协议是因为它非常适合在读写寄存器的模式下使用,原因在于每次读写寄存器值时的数据量较小,不需要复杂的总线协议,只需简单的控制逻辑即可实现。

2、多个通道启用时,传输事务在所有通道内交织,使用循环协议维护通道。事务粒度取决于主机有效载荷大小、页面大小等。AXI4-Lite主接口:实现AXI4-Lite主接口总线协议,主机通过此接口生成读取和写入请求,数据通过PCIe到DMA旁路BAR返回。

3、AXI4-Lite主接口用于实现AXI4-Lite主接口总线协议,允许主机生成32位读取与写入请求。这些请求通过PCIe到DMA旁路BAR接收,读取完成数据返回至主机。AXI4-Lite从接口则负责用户逻辑对DMA内部寄存器的32位读取或写入操作,不支持对PCIe集成块寄存器的访问。

axi4-stream和pcie怎么直接进行数据传输?

1、YUV转RGB转换等关键步骤。随后,数据被缓存在DDR3存储器中,并通过XDMA接口直接发送至PCIe总线。此外,我们还设计了同步HDMI输出功能,确保视频数据在PCIe传输的同时,也能在显示器上实时显示,便于验证传输的正确性和性能。

2、在准备好请求ID并启用通道后,通道的AXI4-Stream接口即可接收数据并执行DMA。在AXI4 MM接口配置中,通过向AXI4 MM接口发出读取请求来分配请求ID。C2H通道在接收到PCIe IP指示的写入请求后,写入请求即告完成。

3、C2H通道:负责卡到主机的DMA传输,数量在配置中控制,未完成传输数由参数配置。在AXI4-Stream配置中,先设置传输详情,数据通过DMA描述符接收。准备好请求ID并启用通道后,通道接口接收数据并向主机执行DMA。在AXI4 MM配置中,读取请求即分配请求ID。与H2C通道类似,请求保持未完成,直至写入完成。

如何解析vivadoxDMA(PCIe)核数据传输原理(双口ram)?

视频输入通过笔记本模拟的HDMI接口,解码和缓存由silicon9134和AXI4总线完成,其中还包含3帧缓存,保证了数据的稳定传输。Vivado工程详解 针对Xilinx的xc7k325tffg900-2开发板,我们使用Vivado 2011进行设计,输入为HDMI,输出为PCIe X8,目标是实现QT上位机的显示试验。

PCIE的实现通常依赖于XDMA,这是一种由Xilinx提供的高性能、可配置的DMA解决方案,适用于PCI Express 0与0的SG模式,并支持AX 4接口或AX-Stream接口。在SG模式下,主机通过构建链表来组织待传输数据,并通过BAR(Base Address Register)将链表首地址传递给XDMA。

在Vivado项目中,通过IP Catalog搜索并添加XDMA IP核到设计中。配置XDMA IP:Basic配置:选择DMA模式。设置基本模式、设备/端口类型。配置PCIe块位置、通道宽度、最大链路速度等参数。设置AXI地址宽度、AXI数据宽度、AXI时钟频率。选择DMA接口选项和AXI4Lite从接口。PCIe ID配置:通常保持默认设置,无需更改。

理论知识:XDMA传输流程图 H2C通道:在vivado配置中设定数量,负责主机到卡的DMA传输。它会根据最大读取请求大小和内部资源拆分请求,保留未完成请求,直到写入完成。读取和写入事务在数据FIFO空间内拆分,PCIe RC块会将完成数据返回给已分配的缓冲器,同时开始向用户接口发出写入请求。

XDMA学习笔记:EP模式

1、在XDMA EP模式的学习笔记中,我们探讨了在alinx AXU4EV-P开发板上使用XDMA进行EP(Endpoint)例程的环境和逻辑结构。首先,使用的工具包括Xilinx自带的驱动和Windows测试软件,以及lspci/setpci等Windows工具。默认配置中,IRQ和CQ/CC接口未被利用,用户逻辑通过AXI-MM接口进行数据传输。

2、本文将主要讲解AXI-Lite总线协议,并以XDMA的部分内容为例进行阐述。通过勾选PCIe to AXI Lite Master Interface,设置默认1MB的空间大小,上位机与FPGA之间即可实现通过PCI-E进行读写寄存器的操作。

到此,以上就是小编对于rapidio传输速率的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏