本篇目录:

如何判断信号是高速还是低速

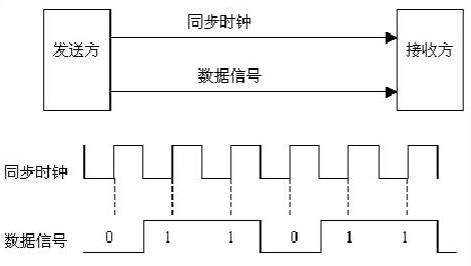

一般而言,在信号传输路径的长度(即信号线的长度)小于信号有效波长的1/6时,可认为在该传输路径上,各点的电平状态近似相同,即低速信号,反之为高速信号。然而,对于极高频信号(如频率在1GHz以上的信号)并不成立,极高频信号的上升沿很缓,上升时间甚至可达信号周期的20%。

高速信号,主要取决于是不是上升沿很陡,也就是说,上升沿越陡,就是个高速信号,反之就是低速信号。

频率,上升沿。根据查询中关村在线显示,频率:高速信号频率高,而低速信号频率低。上升沿:高速信号的上升沿很陡,而低速信号的上升沿很缓。

电平信号的TTL电平定义

ttl电平是指适合于ttl电路工作的电平。TTL电平信号规定,+5V等价于逻辑“1”,0V等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。这是计算机处理器控制的设备内部各部分之间通信的标准技术。

TTL电平是一个基本的数字电子术语,代表着逻辑电平中的两种状态之一。 TTL(Transistor-Transistor Logic)电平,是一种通用的数字电路设计标准,其基本原理是通过晶体管和电阻/电容(RC)电路来实现逻辑门电路的设计和运作。

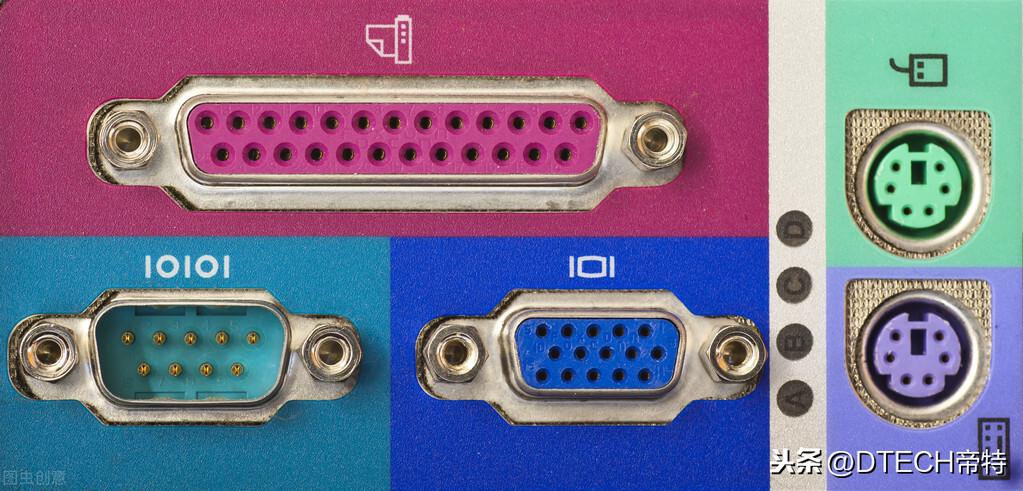

电平标准(电信号)。TTL电平标准是 :低电平为0,高电平为1(对地,标准数字电路逻辑)。RS485是 :正电平为0,负电平为1(对地,正负6-15V皆可,甚至可以用高阻态)。采用差分信号逻辑,更适合长距离、高速传输。

TTL电平是指晶体管-晶体管逻辑电平标准。TTL电平标准是一种在数字电路设计中广泛使用的信号电平标准,特别是在微处理器和微控制器的设计中。TTL电平通过使用双极晶体管来执行逻辑功能,提供开关功能,并有两个可能的电平值,分别表示为高电平和低电平。

TTL电平是一种数字电路中的信号电平标准。TTL电平是一种集成电路逻辑电平,主要应用于计算机硬件和数字电子领域。TTL电平通常被用作处理器和其他电子组件之间的接口信号,因为它们能够处理高速度的数字信号。在计算机系统中,TTL电平也被广泛应用于数据传输和信号处理。

TTL电平是数字电路中常见的一种信号电平,全称为Transistor-Transistor Logic,即为双晶体管门电路。TTL电平的基本含义是,在TTL集成电路中,逻辑0和逻辑1所对应的电压范围。TTL电平的工作原理是通过晶体管与晶体管之间的逻辑电平变化来传递和解释数字信号的。

rs485接口电平是多少

1、将总线上的差分信号的正端A+和负端B-之间接一个10K的电阻,负端B-和地间接一个10K的电阻,形成一个电阻网路。当总线上没有信号传输时,正端A+的电平大约为2V,负端B-的电平大约为6V,即使有干扰信号,也很难产生串行通信的起始信号0,从而增加了总线抗干扰的能力。

2、RS485是 :正电平为0,负电平为1(对地,正负6-15V皆可,甚至可以用高阻态)。采用差分信号逻辑,更适合长距离、高速传输。定义 RS485的电气特性(现在较常用的接口)RS485采用差分信号负逻辑,逻辑1”以两线间的电压差为-(2~6)V表示;逻辑0以两线间的电压差为+(2~6)V表示。

3、一般来说,RS485接口的电平范围在-7V至+12V之间,甚至可以用高阻态。具体来说,逻辑1以两线间的电压差为-(2~6)V表示,而逻辑0则以两线间的电压差为+(2~6)V表示。这种差分信号逻辑使得RS485接口更适合长距离、高速传输,因为它能有效减少信号衰减和噪声干扰。

到此,以上就是小编对于高速信号相关的电路布局需要注意哪些的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏