本篇目录:

- 1、用verilog程序设计一个具有异步清零功能的24进制计数器

- 2、如何用Verilog设计一个异步清0、同步时钟使能和异步数据加载型8位二进...

- 3、verilog编程技巧

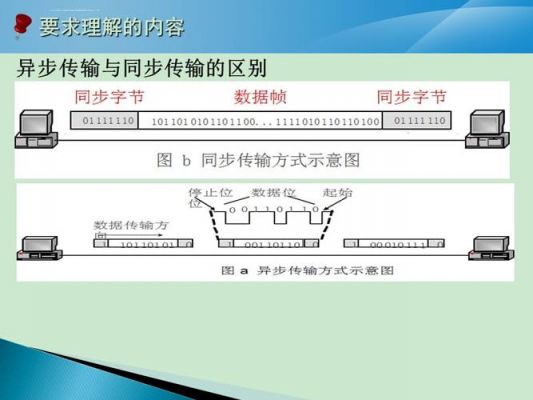

- 4、用verilog程序设计一个具有异步复位功能的24进制计数器

- 5、verilog中d触发器的异步高电平复位是什么意思

- 6、verilog组合逻辑怎么插入buffer?

用verilog程序设计一个具有异步清零功能的24进制计数器

编译,通过后,添加波形文件,如下图所示。保存,点击波形仿真按钮,开始波形仿真,如下图所示。仿真成功,结果如下图所示。波形仿真情况1:使能en及m=1时模23计数仿真结果如下图。

而两位合起来组成24进制计数器,就利用计数24的值产生复位信号,使两片计数器回0,这只能用反馈清0法。一个计数器要改制,只有这两种方法,而这种方法都要用到一个电路上。因此,也只有一种方法来设计。

在jsp或者html中使用jquery发送ajax请求,这里是获取后台的某个接口。只需要修改ajax请求中的async参数即可,async是异步的意思,如果需要设置同步,只需要设置为async=false。

LS90构成24进制计数器 74LS90的进位规则DIGITAL SIGNAL AND DIGITAL CIRCUIT 利用74LS90的清零功能和进位规则设计出60进制计数器。

把一个74161的Q3作为这一级的进位输出端,就是一个八进制计数器。

如何用Verilog设计一个异步清0、同步时钟使能和异步数据加载型8位二进...

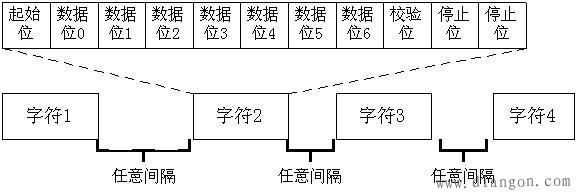

1、在jsp或者html中使用jquery发送ajax请求,这里是获取后台的某个接口。只需要修改ajax请求中的async参数即可,async是异步的意思,如果需要设置同步,只需要设置为async=false。

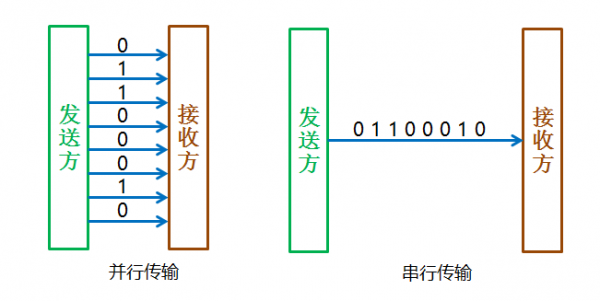

2、在可逆计数器的设计中的错误,两个进程里都有同一个条件判断的话,会产生并行信号冲突的问题。同一个信号不允许在多个进程中赋值,否则则为多驱动。

3、如下,该D触发器输入为clk,rst_n,set,d。

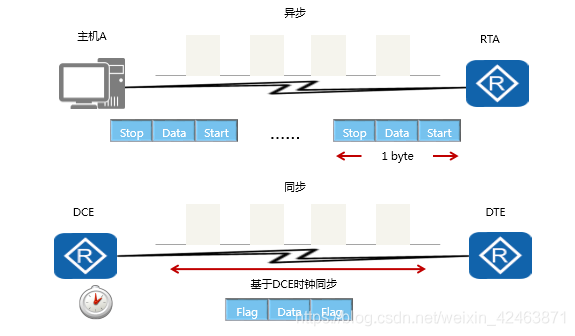

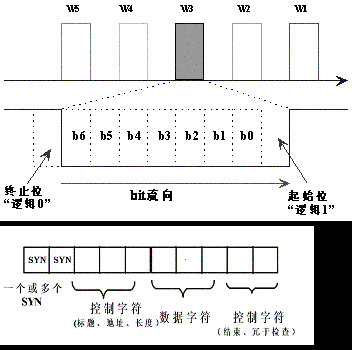

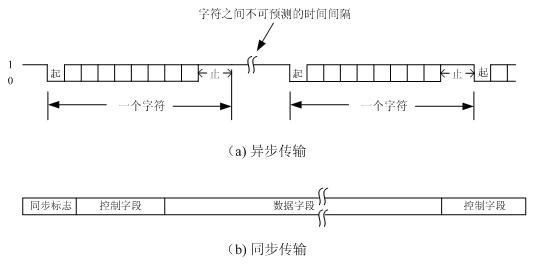

4、verilog可以利用同步复位和异步复位来给时序逻辑电路清零,同步复位是需要有时钟,在时钟沿来的时候检测复位信号的值,如果复位信号有效,则对电路清零。

5、QA,QB,QC.QD为输出端。十进制即为从0-9九种状态。RD是异步清零端,就是任何时候当RD为0时,QA,QB.QC.QD回到0重新开始计数。故让计数到10的时候,QD,QC,QB,QA为1010时,让RD为0 ,于是用一个与非门。

verilog编程技巧

两分法,用按位或判断是否全零。例如结果5bit,若输入的高16bit全零,结果的最高位就置0,否则置1,依次两分。

用mask提取通道信息,滤掉flag中的无效信息。

A A_LianJie(a1 (b1),a2 (b2))这样就把我们需要连接的两个模块连到一起了,信号多了也是一样的,继续把信号对应填到括号里就行了。如果还有不明白的,可以继续问我。verilog设计我做了2年了,呵呵。

数据文件写好后,就要编写Verilog测试模块读取该文件并对模块进行测试了。在项目上右键,点击New Source,接着选择Verilog Test Fixture,输入文件名并继续,选择待测模块,接着创建文件。

第三点:楼主确实有这么点不完善,不过有些时候可以预先确知某些信号同时发生也可以不考虑的。最后的你建议,先学C再改verilog,个人意见非常不赞同。很多软件工程师特别喜欢把写软件哦思维带到硬件描述语言中来。

用verilog程序设计一个具有异步复位功能的24进制计数器

编译,通过后,添加波形文件,如下图所示。保存,点击波形仿真按钮,开始波形仿真,如下图所示。仿真成功,结果如下图所示。波形仿真情况1:使能en及m=1时模23计数仿真结果如下图。

”、CP脉冲上升沿作用后,计数器加1。74LS161还有一个进位输出端CO,其逻辑关系是CO=Q0·Q1·Q2·Q3·CET。合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

LS90就是十进制计数器,可以做十位,个位计数器。而要解决是问题是个位向十位进位,逢24回零,实现24进制计数,最大数是23。

进制计数器,就是从0开始计数,计数到301后,再从0开始重新计数,就像十进制计数一样,从0开始计数,计数到9后回到0重新开始计数。

verilog中d触发器的异步高电平复位是什么意思

1、触发器的异步端一般是指异步清零端或异步置位端。清零端的作用:在该端加上有效电平或有效脉冲跳变(多数是高电平或正跳变有效,如果该端有个小圈则是低电平或负跳变有效)则时序电路的输出端输出无效电平。

2、end异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

3、输入端D前面标有一个“1”,表示这个输入端受时钟信号的影响,而在置一端和置零端S和R的前面没有标注1,说明这两个输入端不受时钟信号的影响,也就是说他们是异步置一和异步置零端。

verilog组合逻辑怎么插入buffer?

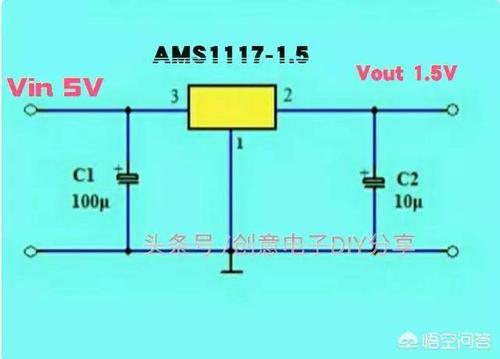

1、VHDL中的buffer端口是带有反馈的输出端口。在Verilog HDL中,没有区分输出端口是否带有反馈,所以在Verilog HDL中,直接声明为output就可以了。

2、组合逻辑电路设计的一般步骤 在数字电路中,根据逻辑功能的不同,我们可以将数字电路分成两大类,一类叫做组合逻辑电路、另一类叫做时序逻辑电路。本次主要讲解组合逻辑电路的原理、应用和Verilog实现。

3、在Verilog中,组合逻辑移位赋值时,如果使用的是16位的赋值操作符(例如=),而目标变量只有8位的宽度,那么高8位会丢失是因为Verilog会自动截断目标变量的赋值结果,以适应目标变量的宽度。

4、verilog赋值有塞赋值(=)和非阻塞赋值(=)两种赋值方式。其中,组合逻辑电路:使用阻塞赋值(“=”);时序逻辑电路:使用非阻塞赋值(“=”)。

到此,以上就是小编对于异步传输的单位的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏