本篇目录:

AXI的AXI的特点

AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

Axi-p带混二,绝对够用,保证准度的同时又有不错的弹性,可以打出一些极限杆法,我本人就是这个组合,全台低杆可以拉到底库,3500买来的,等杆子熟悉了,再去升级exc。

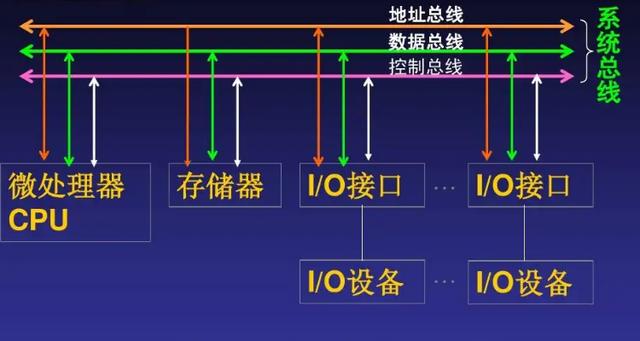

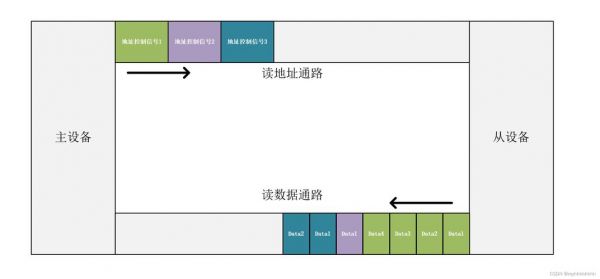

AXI能够使SoC以更小的面积,更低的功耗,获得更加优异的性能。AXI获得如此优异性能的一个主要原因,就是它的单向通道体系结构。单向通道体系结构使得片上的信息流只以单方向传输,减少了延时。

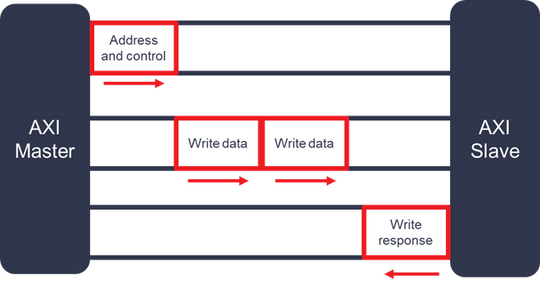

AXI的是5通道设计的,读写地址分开,吞吐量大,第一个版本叫AXI3,后来更新到AXI4,支持最多256beat的long burst和QoS。AMBA 4之后ARM还发布了AMBA CHI,以便更多处理器通过环形总线互联,实现环形总线上的数据传输。

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,需要加入一个AXIInterconnect模块,也就是AXI互联矩阵,作用是提供一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。

AXI3和AXI4的区别有哪些?

AxLOCK不再支持“锁定”传输。由于不再支持写入数据传输的交错,因此AXI4没有WID信号。AxCACHE [1]重命名为“可修改”位。定义为描述各种AxCACHE编码的“内存类型”,解释系统应如何处理这些传输。

AXI的是5通道设计的,读写地址分开,吞吐量大,第一个版本叫AXI3,后来更新到AXI4,支持最多256beat的long burst和QoS。AMBA 4之后ARM还发布了AMBA CHI,以便更多处理器通过环形总线互联,实现环形总线上的数据传输。

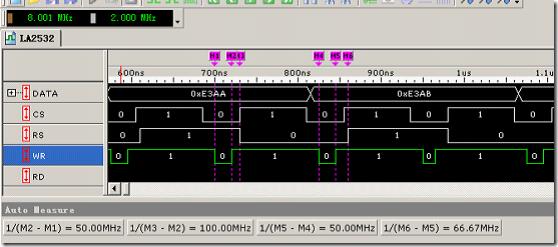

axi 3的要求是brespond之类的在data channel完成以后,对于aw和data顺序没有要求,但是一般来说即使接受了data也是需要等aw的,因为需要地址。axi4的话,明确要求brespond在data和aw channel完成之后。

fpga读16位ddr3和32位ddr3

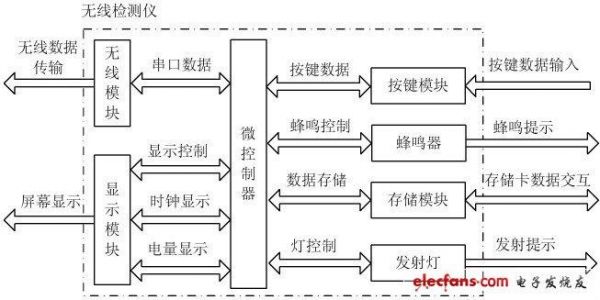

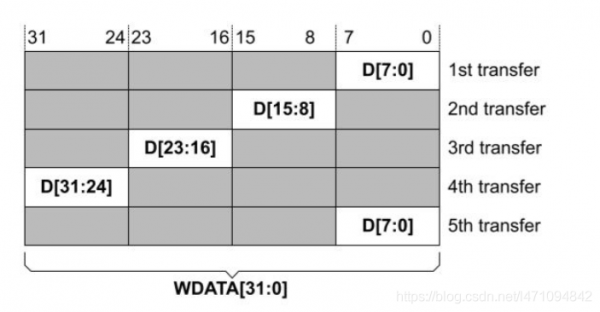

AXI4-Stream:用于高速数据流传输,非存储映射接口。AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite 为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。

是一样的,一般用两片16位的DDR3构成32位存储器,这是两片DDR3的地址线和控制信号是共用的,但两片DDR3的数据线(DQ/DQS/DM)分别引到FPGA的不同的引脚。

DDR芯片安装不当。无法识别芯片类型或者驱动程序不正确等,还有可能是晶振安装错误或者与FPGA板不兼容等原因导致的。如果出现FPGA初始化DDR失败情况,建议通过检查DDR芯片、晶振等硬件设备以及驱动程序来解决问题。

fpga图像传输可以不用ddr3,可以独自完成图像传输的工作。DDR3是一种计算机内存规格。属于SDRAM家族的内存产品,提供了相较于DDR2SDRAM更高的运行效能与更低的电压,是DDR2SDRAM的后继者,也是现时流行的内存产品规格。

DDR3是外部存储器,FPGA只是提供访问外部存储器的端口和控制器,一定是独立的。你说的读和写是不是对于一个外部DDR3存储器而言呢?对于同一个外部存储器,这当然不是问题,因为存储器肯定是要读和写的。

到此,以上就是小编对于axi突发传输怎么实现的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏