本篇目录:

- 1、为什么说FPGA片内同步RAM的好处是带宽可以做得很大,可以采用流水线结构...

- 2、谁知道cpld或者fpga能控制的时延精度最高能达到多少?依据是什么??_百度...

- 3、fpga中异或门延时多少时间

- 4、FPGA与CPLD的区别在哪?

- 5、如何在FPGA内部产生准确的灵活的延时?

- 6、fpga实现延时如何实现?

为什么说FPGA片内同步RAM的好处是带宽可以做得很大,可以采用流水线结构...

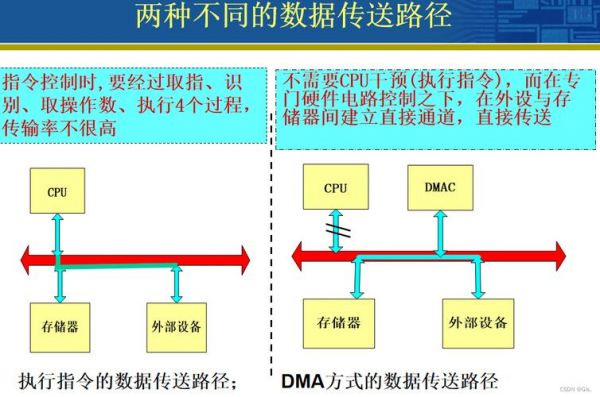

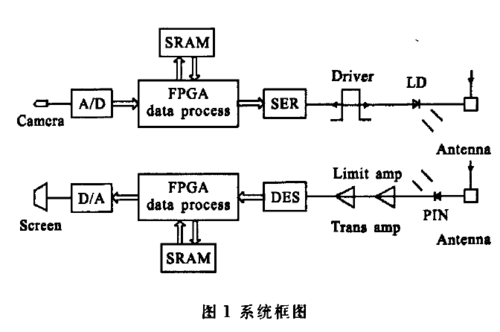

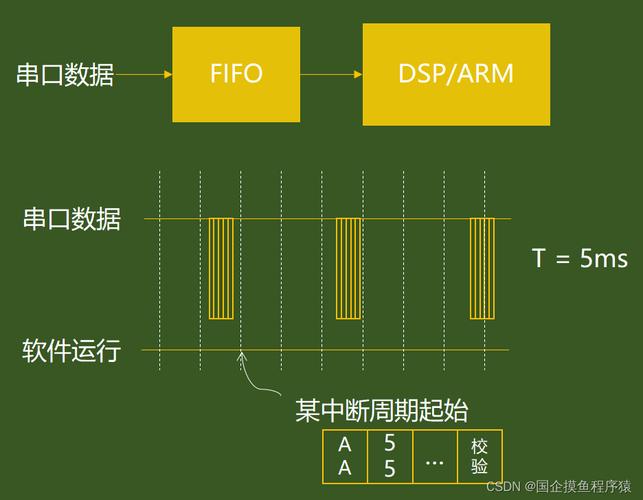

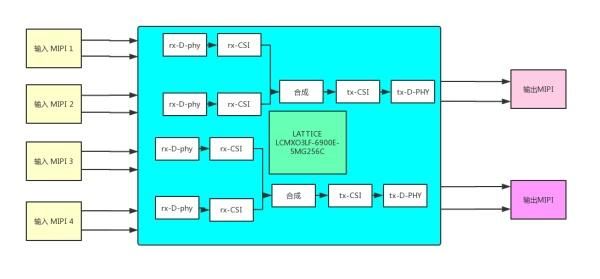

1、FPGA具有可编程的延迟数字单元,在通信系统和各类电子设备中有着比较广泛的应用,比如同步通信系统,时间数值化系统等,主要的设计方法包括数控延迟线法,存储器法,计数器法等,其中存储器法主要是利用FPGA的RAM或者FIFO实现的。

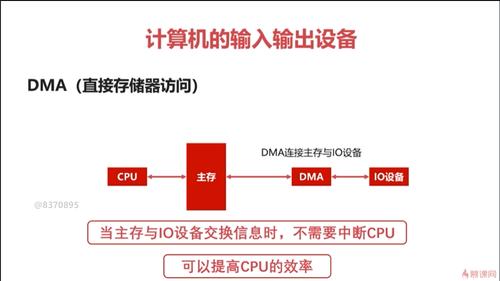

2、由于构建由寄存器和LUT组成的大型RAM的密度比SRAM块低100倍左右,因此还需要具有更密集的片上存储。此外,在现场可编程门阵列上实现的应用程序的RAM要求差异大不相同。

3、就相当于一个人在一条生产线上,每一个动作都要由这个人去做,他只有把5个动作都做完才能去做下一件事情。

4、去除了一些普通用户难以用及的功能(如ECC内存、双CPU支持等)后,增加了对高速同步存储器SDRAM的支持,支持168线内存插槽和内存条;在结构上恢复了4片芯片结构。

5、在数据中心,FPGA相比GPU的核心优势在于延迟。FPGA为什么比GPU的延迟低很多?本质上是体系结构的区别。FPGA同时拥有流水线并行和数据并行,而GPU几乎只有数据并行(流水线深度受限)。

6、DSP内部采用程序和数据分开存储和传输的哈佛结构 ,具有专门硬件乘法器,广泛采用流水线操作,提供特殊 的DSP指令,可用来快速的实现 各种数字信号处理算法,加之集成电路 的优化设计,速度甚至比最快的CPU还快数倍。

谁知道cpld或者fpga能控制的时延精度最高能达到多少?依据是什么??_百度...

也就是你执行一次时延操作所用的时间即时延精度就是0.24us;如果是双周期指令就加倍。

因为CPLD的延时是可以估算的。CPLD结构简单,因此,实现的逻辑简单的话,每个环节的延迟是可以事先计算好的;复杂逻辑照样不好预估,CPLD也有布线捷径;另外,CPLD因为绕的远,某些布线延迟比较大。

CPLD和FPGA包括了一些相对大数量的可以编辑逻辑单元。CPLD逻辑门的密度在几千到几万个逻辑单元之间,而FPGA通常是在几万到几百万。CPLD和FPGA的主要区别是他们的系统结构。CPLD是一个有点限制性的结构。

fpga中异或门延时多少时间

具体延迟时间与FPGA芯片采用的工艺有关,有些型号时间短些,有些就长一些。

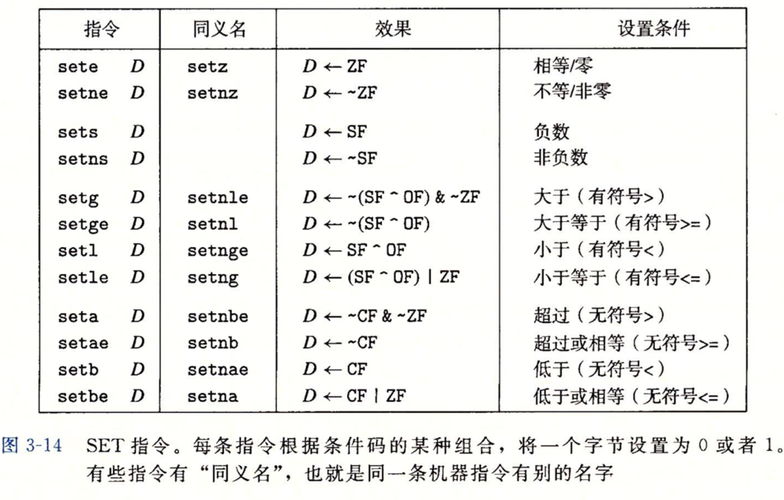

字面意思理解,所谓约束,就是加上一些条,说白了就是通过时序约束对逻辑综合器提出你的要求,然后综合器根据要求进行布局布线。

单片机延时功能块中延时时间可分为三个级别如下:一级是小于10US的延时。二级是大于10US的延时。三级微秒级别。

器件中单稳触发器作用是不管触发信号持续多长时间,只固定维持外围阻容给定的一段时间就恢复触发前状态,外围电阻电容决定单稳时间,因为触发是由边缘触发,上升或下降沿。

FPGA与CPLD的区别在哪?

1、)、在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FP GA可在逻辑门下编程,而CPLD是在逻辑块下编程。

2、区别是:CPLD主要是由可编程逻辑宏单元(LMC,Logic Macro Cell)围绕中心的可编程互连矩阵单元组成。FPGA通常包含三类可编程资源:可编程逻辑功能块、可编程I/O块和可编程互连。

3、⑤CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法复杂。⑥CPLD的速度比FPGA快,并且具有较大的时间可预测性。

4、从内部结构来看,CPLD是 Product term(基于乘积项), FPGA是Look up Table(基于查找表);从程序存储来看, CPLD是内部EEPROM/FLASH SRAM,FPGA是外挂EEPROM。

5、CPLD与FPGA在结构方面的区别:CPLD是粗粒结构,这意味著进出器件的路径经过较少的开关,相应地延迟也小。因此,与等效的FPGA相比,CPLD可工作在更高的频率,具有更好的性能。

6、③在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FP GA可在逻辑门下编程,而CPLD是在逻辑块下编程。

如何在FPGA内部产生准确的灵活的延时?

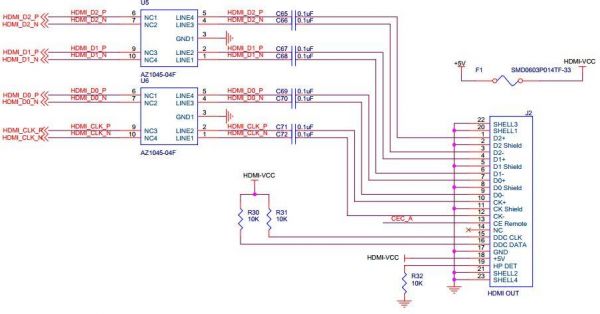

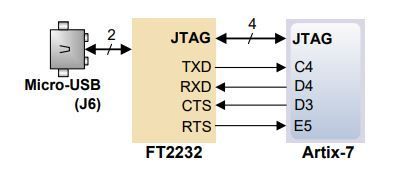

1、)利用走线的延时。可以用约束的方法,让这个信号的走线人为绕远。这种方式可以延时几到几十纳秒,但是随着芯片的批次不同以及芯片工作温度的变化,这个延时是不精确的;2)利用时钟往后推。

2、如果是FPGA的话,建议用PLL把时钟提高。然后用这个信号去采样22kHz的信号,用计数器记录信号电平改变的时间,记录相邻几次的值(总时间大于延迟时间就可以了),然后加上延时,从新计数输出。

3、有赋值符号 = 就可以了,这个符号是延迟一个时钟的。而 = 是不延迟的。

4、不同的FPGA门延时会有一些区别看你用的FPGA是多少,一般用门延时来做的话可以达到机个NS的延时,当然它也有最小延时的限制那就是你的门延时。一般来说用VHDL很容易实现计数器做的延时也就是第一种。

5、不要只想着VHDL还是Verilog。作为一个电路工程师,你必须了解底层的逻辑,RTL级是如何实现的。9ms的延时想在FPGA内部实现唯一可行的办法就是外接一个低频的时钟,周期在毫秒级的,利用这个时钟把信号往后打几个时钟周期。

fpga实现延时如何实现?

1、用ALTERA公司的MaxplusII开发FPGA时,可以通过插入一些LCELL原语来产生一定的延时,但这样形成的延时在FPGA芯片中并不稳定,会随温度等外部环境的改变而改变,因此并不提倡这样做。

2、有赋值符号 = 就可以了,这个符号是延迟一个时钟的。而 = 是不延迟的。

3、如果是FPGA的话,建议用PLL把时钟提高。然后用这个信号去采样22kHz的信号,用计数器记录信号电平改变的时间,记录相邻几次的值(总时间大于延迟时间就可以了),然后加上延时,从新计数输出。

到此,以上就是小编对于fpga布局布线最大传输延时是多少的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏