本篇目录:

求TMS320c6416的原理和使用方法

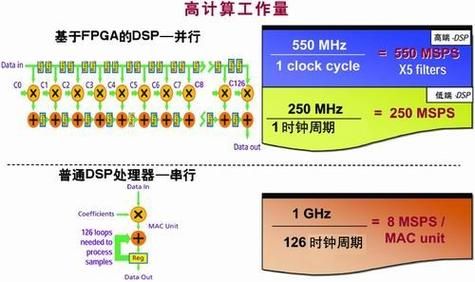

在没有采用TMS320C6416的系统中,两种译码可以由DSP软件来实现,但这会大大降低DSP处理其它业务的能力;译码也可以由外部FPGA/ASIC硬件实现,但这会增加单板器件的密度和功耗。

由于S3C4510B中没有完全符合TMS320C6416 HPI接口时序的外部接口可以直接使用,因此选用S3C4510B中时序最接近HPI接口时序的外部I/O接口与TMS320-C6416进行连接。TMS320C6416与S3C4510B接口电路如图2所示。

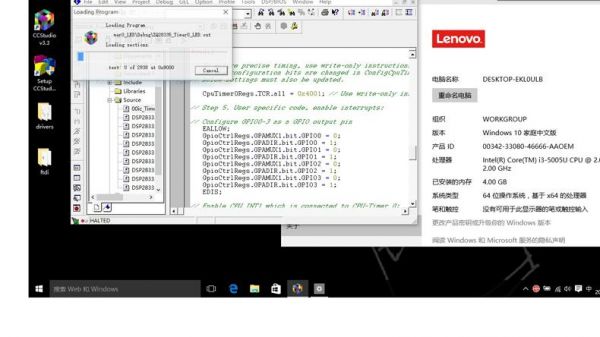

软仿真可以不写终端向量表,在编译器里设置复位后跳到c_int00()就可以,但脱离仿真器的时候就不行,复位后就直接跳到0地址开始执行程序了,如果是c语言写的程序,没有初始话的过程就无法运行。

TI 公司的DSP 在全球市场上的占有率在一半以上,而TMS320C6416 则是其最高端的产品,具有主频高、双套外部地址和数据总线等特点,非常适合用于图像处理等领域,但是在多芯片集成处理上AD 公司的DSP 芯片性能更好一些。

TMS320C6416是TI公司推出的高速定点DSP,它拥有处理能力强大的CPU、高达1 MB的RAM、丰富的外设接口。

FPGA中数据如何高速传到DSP

在同一块板子上可以使用EMIF,DMA,PPI传输,速度慢一点的可以IIC,SPI,如果不在一块板子上,速度慢可以RS485,速度快得可以使用LVDS传输。

一般DSP通过EMIF接口与FPGA连接,也就是通过EMIF接口读取FPGA内的数据,然后存入到DSP外挂的DDR3中了。

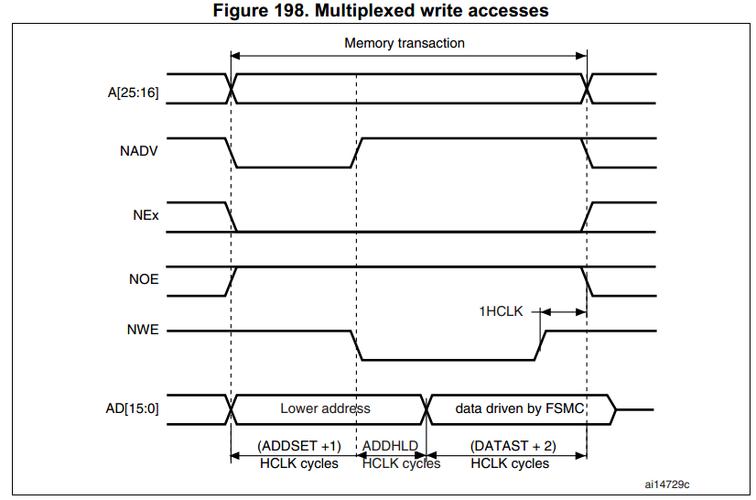

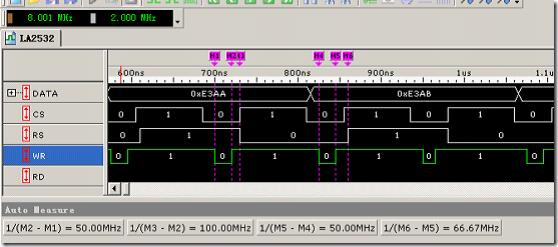

找一款简单的dsp芯片,比如ti的54系列,看看emif接口,fpga可以跟emif挂接,然后用emif的读写来操作fpga内部逻辑。不过,fpga的逻辑时序要符合dsp的emif接口时序。先把dsp看好。

,首先,你也需要对dsp有一定的了解,编写dsp接受数据小程序,实现的功能:当dsp接收到fpga的数据后,如果正确,可以让dsp控制对应的指示灯管脚为“1”或“0”,这样就可以控制灯的亮与灭来判断dsp接受的数据是否正确。

请教emif口读写同步存储器件的速度问题

1、嵌入式简而言之,就是微微型的计算机。特点就是一个“小”。应用非常广泛,通信,航空,工业,等等,无处不在。

2、SDRAM(Synchronous DRAM,同步动态随机存储器),即数据的读写需要时钟来同步。其存储单元不是按线性排列的,是分页的。DRAM和SDRAM由于实现工艺问题,容量较SRAM大。但是读写速度不如SRAM。

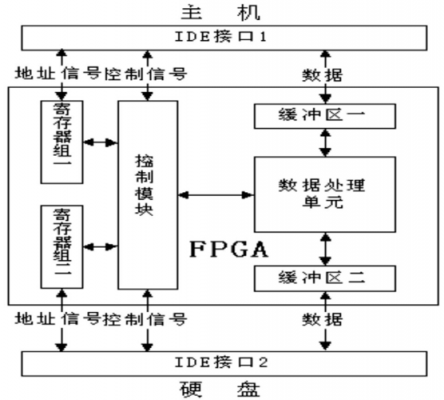

3、一般来说,EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM等)的连接。. 在本应用指南中,EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

数据传送的一、数据传送的整体设计

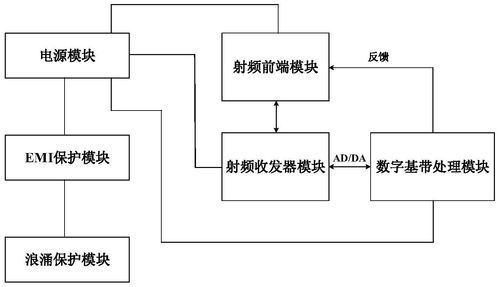

综合考虑到测试系统实时性和可靠性的要求,选择以太网口作为数据传送总线变换器与上位机的数据转发接口,以高速串口作为控制口,采用FPGA+DSP+ARM的架构作为实时信息处理平台。数据传送总线变换器的系统框图如图1所示。

计算机与外设之间进行数据传送有三种基本控制方式:查询方式、中断方式和DMA方式。 1.查询方式 查询方式是通过执行输入/输出查询程序来完成数据传送的。

(11)由MAX3110E将该串行数据流转换成标准异步串行数据传送给串口设备,至此,一个简要的由IP数据包传送至串口设备的流程基本上如此,在这里限于篇幅,我们只介绍了一个单向的通路情况,没有对各个旁支情况作介绍。

传送到以 RR5 为首地址的目的 RAM 区。

到此,以上就是小编对于fsmc总线速度的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏