本篇目录:

什么是总线周期?

总线周期通常指的是CPU完成一次访问MEM或I/O端口操作所需要的时间。一个总线周期由几个时钟周期组成。一条指令包括三个操作:取值、分析、执行》所示,执行周期为一条指令的开始到下一条指令的开始时间。

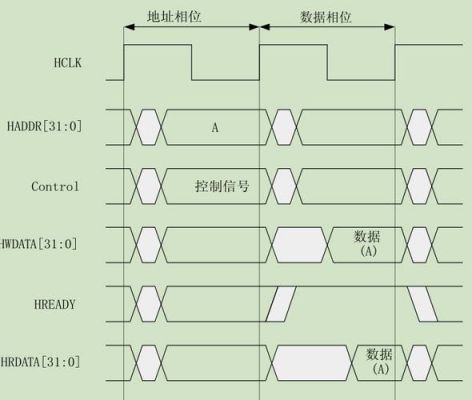

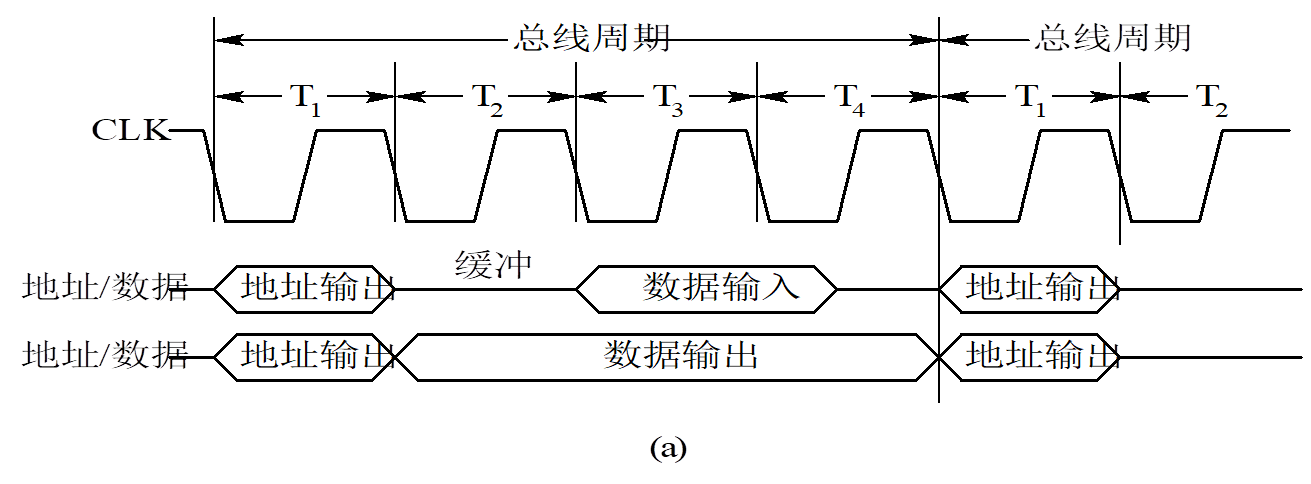

通常把CPU通过总线对微处理器外部(存贮器或I/O接口)进行一次访问所需时间称为一个总线周期。一个总线周期一般包含4个时钟周期,这4个时钟周期分别称4个状态即T1状态、T2状态、T3状态和T4状态。

总线周期:cpu完成一次访问存储器或I/O接口的时间。一个总线周期包含4个时钟周期(T1~T4)。指令周期:完成一次指令的时间。一个指令周期由一个或多个总线周期组成。从而用新内容21代替PC原先的内容25。

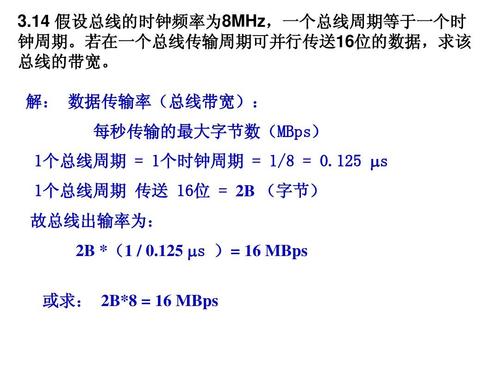

总线周期是指CPU与外部设备之间进行数据传输的时间间隔,包括了地址传输、数据传输和控制信号传输等。总线周期的主要作用是实现数据的读取和写入操作,以及控制外部设备的工作。

指令周期:是指执行一条指令所占用的全部时间,一个指令周期通常含1~4个机器周期。总线周期:通常把CPU通过总线对微处理器外部(存贮器或I/O接口)进行一次访问所需时间称为一个总线周期。

什么是总线?简要说明AB、DB、CB的含义及其性能?

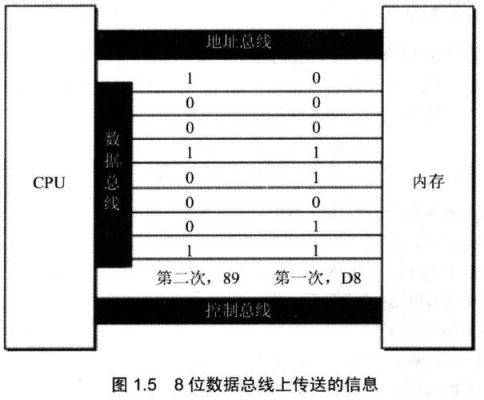

“数据总线DB”用于传送数据信息。数据总线是双向三态形式的总线,即他既可以把CPU的数据传送到存储器或I/O接口等其它部件,也可以将其它部件的数据传送到CPU。

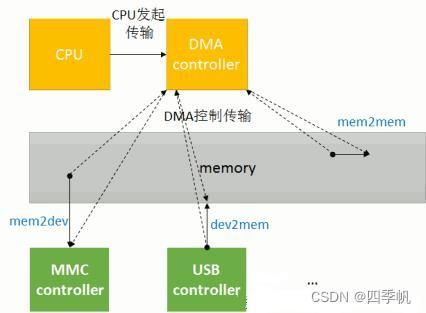

地址总线(AB):地址总线用来传送地址信息。CPU地址线数目决定了CPU选址的内存范围。地址信号一般由CPU发出,当采用DMA方式访问内存和I/O设备时,地址信号也可以由DMA控制器发出。

数据总线DB(Data Bus)数据总线DB用于传送数据信息。地址总线AB(Address Bus)地址总线AB是专门用来传送地址的。控制总线CB(Control Bus)控制总线CB用来传送控制信号和时序信号。

数据总线DB用于传送数据信息。数据总线是双向三态形式的总线,即他既可以把CPU的数据传送到存储器或I/O接口等其它部件,也可以将其它部件的数据传送到CPU。

⑴数据总线DB(Data Bus):用于CPU 与主存储器、CPU 与I/O 接口之间传送信息。数据总线的宽度(根数)决定每次能同时传输信息的位数。因此数据总线的宽度是决定计算机性能的主要指标。计算机总线的宽度等于计算机的字长。

每个总线包含的时钟周期数

1、一个总线周期一般包含4个时钟周期,这4个时钟周期分别称4个状态即T1状态、T2状态、T3状态和T4状态,必要时,可在TT4间插入一个至数个Tw。

2、同步传输周期包含的时钟周期是固定的,就4个,而半同步和异步传输肯定是大于4个。不能再少了。这不是做数学题,想怎么改怎么改。

3、6的基本总线周期为4个时钟周期,每个时钟周期间隔称为一个T状态;T1 状态:BIU将RAM或I/O地址放在地址/数据复用总线(A/D)上。

4、总线周期:cpu完成一次访问存储器或I/O接口的时间。一个总线周期包含4个时钟周期(T1~T4)。指令周期:完成一次指令的时间。一个指令周期由一个或多个总线周期组成。从而用新内容21代替PC原先的内容25。

5、一个基本的总线周期通常包括 4 个时钟周期即t1,t2,t3和t4 。t1状态:cpu把要访问的存储单元或i/o端口的地址输出到地址总线(a0~a19)上。主频为5 mhz,时钟周期为200 ns。

6、总线周期是 微处理器是在时钟信号CLK控制下按节拍工作的。8086/8088系统的时钟频率为77MHz,每个时钟周期约为200ns。由于存贮器和I/O端口是挂接在总线上的,CPU对存贮器和I/O接口的访问,是通过总线实现的。

到此,以上就是小编对于总线的数据传送速率的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏