本篇目录:

- 1、如何用VHDL实现两个双向端口之间的数据传输

- 2、80分帮忙解释程序

- 3、那位大哥知道“可预置的双向计数器”的VHDL语言设计

- 4、试用VHDL描述一个控制端为低有效的反相输出的三态门电路

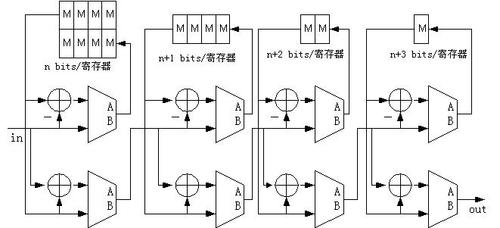

- 5、困扰我半个月的CPLD双向通信IO口问题。下图为1对1的链接,我要用CPLD三...

如何用VHDL实现两个双向端口之间的数据传输

1、个PROCESS运行完毕后才开始生效。VHDL中的信号代表的是逻辑电路中的逗硬地连线,既可以用于电路单元的输入/输出端口,也可以用于电路内部各单元之间的连接。实体的所有端口都默认为信号。

2、你要3选1,但是双向口描述的时候建议在参考上面结构的同时,把选择信号KE嵌套到if里去&一下,不要用case语句。VHDL我不熟,但是verilog里双向口控制信号加一级case语句有时候会出问题。

3、不能为两个输出端口分配同一个引脚。但是,可以这样设计输出端口:将该输出端口声明为决断信号(例如std_logic类型),也就是多驱动源信号。

80分帮忙解释程序

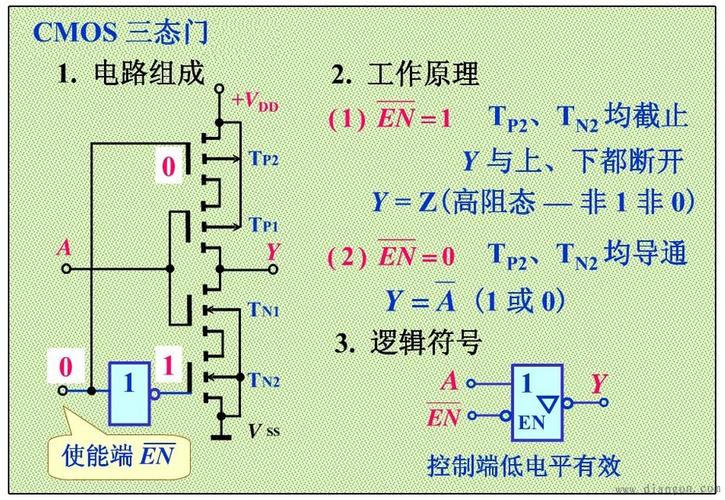

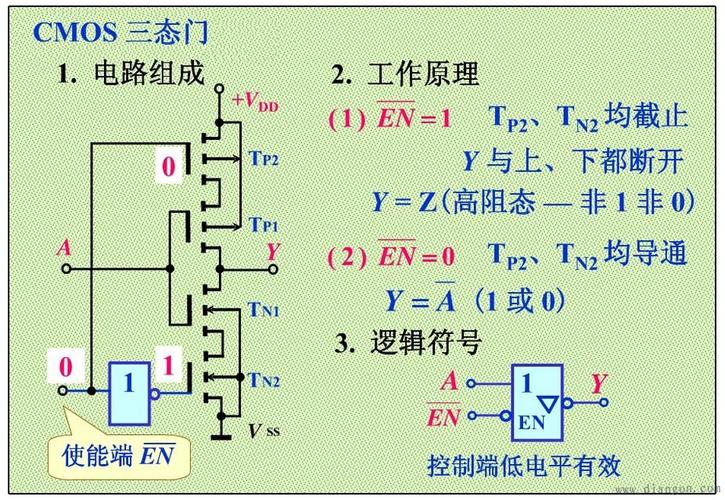

1、只要分析一下输入输出信号的意义,看看process中信号之间是如何赋值的,还是很好理解的,只有程序2的逻辑稍复杂一点。比如第一个,en=1时把信号a传输给b和D,en=0时b输出高阻,此即三态门逻辑。

2、程序的词语解释是:程序chéngxù。(1)数字计算机的编码指令的次序。(2)处理业务(如审议机构的业务)既定方法。(3)事情办理的先后次序。程序的词语解释是:程序chéngxù。(1)数字计算机的编码指令的次序。

3、计算机程序是一组计算机能识别和执行的指令,运行于电子计算机上,满足人们某种需求的信息化工具。

4、return 0;} //程序结束,自动释放对象,调用派生类对象的析构函数。

那位大哥知道“可预置的双向计数器”的VHDL语言设计

1、摘?? 要:本文介绍了可编程定时器/计数器8253的基本功能,以及一种用VHDL语言设计可编程定时器/计数器8253的方法,详述了其原理和设计思想,并利用Altera公司的FPGA器件ACEX 1K予以实现。

2、VHDL语言实现 十进制同步减法计数器(异步清零、同步预置、下降沿触发、带借位输出BO端)。原程序如下,改程序已经通过仿真,仿真结果见图,输入D的值设为3,同步置位后,输出Q=D=3,功能实现。

3、VHDL语言的设计主要有三个设计方向:一是模块设计,信号输出后,进行信号转换,同时对信号进行完整存储;第二设计模块有效采集各种脉冲输入模块数据,方便产生计数器、定时器等控制信号。

4、我来帮你手写吧,写一个计数器,从0计数到4095,然后到4095的时候,产生一个高电平,可以让这个高电平去控制一个LED,让他亮一下(或者一小段时间,这个通过另外一个定时器,可以自由控制),以显示已经计到了。如下。

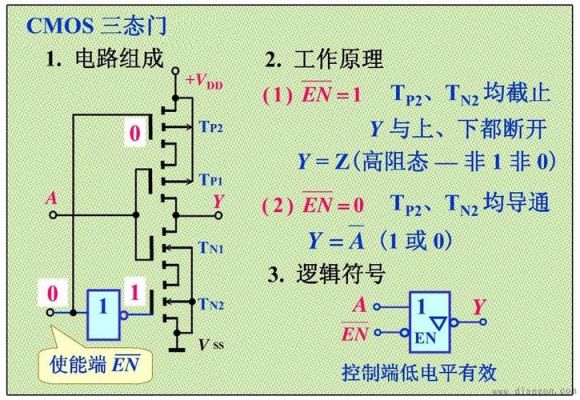

试用VHDL描述一个控制端为低有效的反相输出的三态门电路

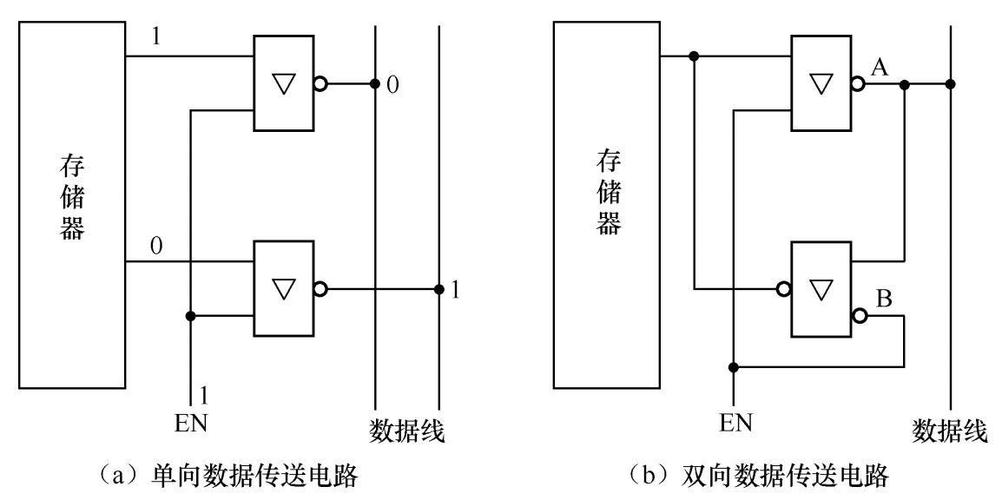

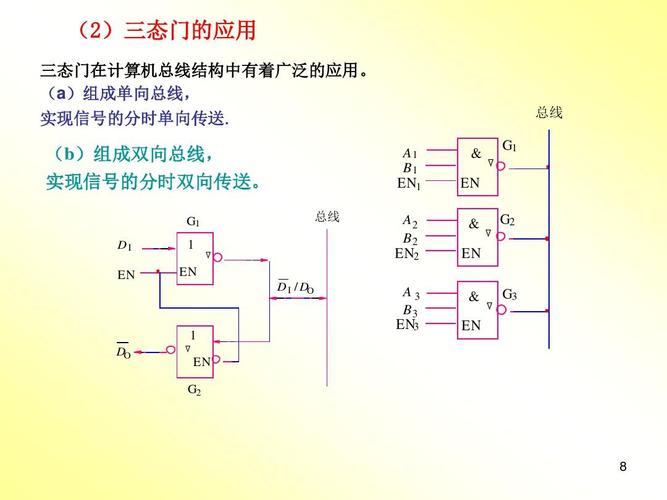

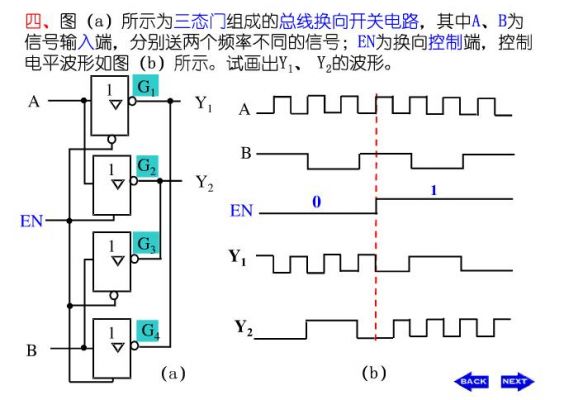

利用三态门]还可以实现数据的双向传输,其中门G1和门G2为三态反相器,门G1高电平有效,门G2低电平有效。

c = a ? b : 0; 当a成立时,就把b赋值给c,否则就把0赋值给c,这就是一个三态门电路。

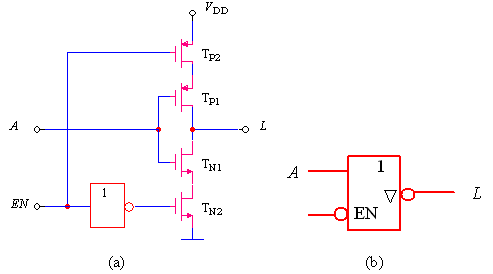

相当于没有接在总线上,不影响其它器件的工作。三态门都有一个EN控制使能端,来控制门电路的通断,要看使能控制端是高电平有效,还是低电平有效,只有在使能控制端有效时,输入端的状态才有效。

双向口有固定描述格式,添加输出Z的描述,否则综合不出来三态门的。

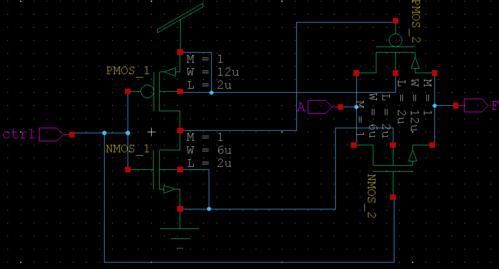

困扰我半个月的CPLD双向通信IO口问题。下图为1对1的链接,我要用CPLD三...

你要3选1,但是双向口描述的时候建议在参考上面结构的同时,把选择信号KE嵌套到if里去&一下,不要用case语句。VHDL我不熟,但是verilog里双向口控制信号加一级case语句有时候会出问题。

单片机与CPLD可以直接相连,但是要注意电平要一致!一般的CPLD的IO口电平为3V的,所以单片机要选那种3V的低压型的,来保证IO口电平一致。实在不行的话,单片机IO口与CPLD之间要加电平转化芯片。

...不是必须带有CPLD的,CPLD一般是由来扩展I/O口的。上面端口定义应该和CPLD有关,port3002 。

DSP以寄存器的方式来控制CPLD的IO口:IO口的对应DSP里面的寄存器,有自己的地址。DSP通过对这个地址的寄存器操作来控制IO口。

到此,以上就是小编对于三态门实现数据的双向传输的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏