本篇目录:

华为2019数字芯片设计笔试题目和解析(单选第一部分)

1、野兽模式下可达最高约38W,带来越级性能表现; 3mm键程键盘经过全面优化,让敲击感超越数字,配合耐磨防污键帽涂层,手感细腻,输入再提速;内置联想轩辕AI智能芯片,配合新一代TOF传感器和IR摄像头,带来更快更准的人脸识别体验。

2、计算机基础模拟试题填空题 计算机的逻辑元件采用大规模、超大规模集成电路的时代是第___代。 计算机中___的主要功能是存放数据和程序。 计算机软机系统包括___和___。

3、年9月27日公司互动平台回复公司目前有两件数字货币相关专利,一件为外观设计专利“闪存盘(冷钱包)”,该专利已获授权;另一件为发明专利”数字货币钱包、交易方法、交易系统和计算机存储介质“,该专利目前正处于实质审查阶段。

时钟模块接单片机哪个接口

1、单片机系统的时钟电路应该接单片机的(119 两个)引脚。

2、是DS12C887呀。那是总线接口,首先也要画一条总线,然后给总线加网络标号D[0..7],注意,[ ]括号内是两个小数点。再与单片机用8条线也P1口连接,再分别给每条导线加网络标号。见下图。

3、图中的pb0 pb1 pb2 分别接单片机的p0 p1 p2 即可, 你也可以接其他的i/o口这个没有固定的接法。

4、SCLK 接 SCLK DATA 接 I/O CE 接 RST 如果要按照DS1302的引脚命名,单片机的DATA可以改成I/O,CE可以改成RST,这样程序看起来就更直观一些。

5、另外一种就是来源于单片机的内部时钟源,但需要外部接晶体振荡器(接在XTAL0和XTAL1端)和电容,这两个引脚的时钟源是可以输出到外部的,具体的使用应该还需要先接上分频器再使用,和一般的时钟源差不多。

6、串行口工作在方式0时输出,串行口以方式0发送时,数据从RXD端串行输出,TXD端输出同步时钟信号。串行口定义方式0并置位REN后,启动以方式0接收时,此时以RXD端为数据输入端,TXD端输出同步时钟信号。

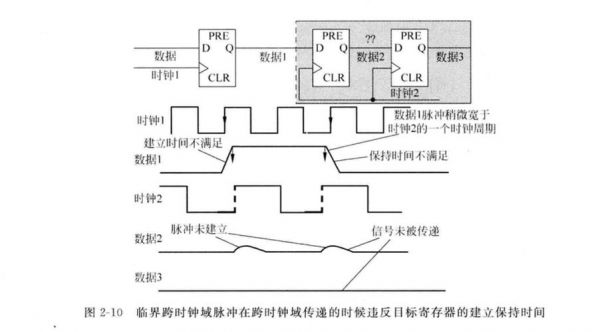

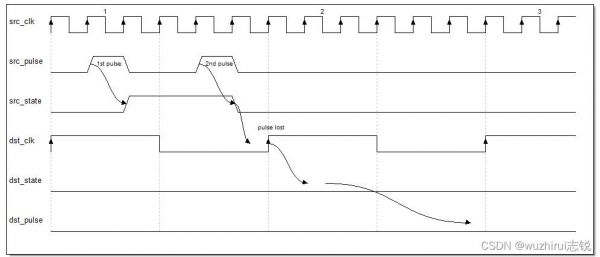

跨时钟域设计

1、该信号从一个时钟域进入到另一个时钟域,由于Td存在传输延时,DA1和DA2到达CLK_B的时间不同,导致一级触发器的触发时钟沿不同,最后导致Fsm1_en和Fsm2_en也存在相位差。这种情况就是多个信号聚合成一个信号。

2、不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。

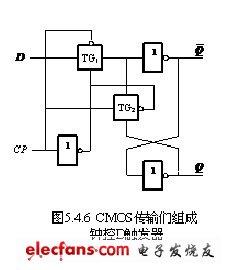

3、) 采用两级D触发器缓存,把“xreq”信号同步到接收器的时钟域“yclk”上,得到“yreq2”信号,当采样到yreq2有效后,将数据锁存到系统y的总线上,同时接收器发出“yack”信号(相应信号)。

4、一般情况下,设计过程中需要尽量使用同步电路,避免异步电路和跨时钟域的情况。在无法避免的情况下,也因采取一些措施去尽量减少亚稳态的产生几率。

5、IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从 全局时钟管脚输入的信号必须经过IBUFG单元,否则在布局布线时会报错。

g703接口的64kbit/s接口

(1)对于发送和接收两个方向,都有三种信号通过接口:64kbit/s信息信号64kHz 定时信号8kHz 定时信号(2)三种接口类型同向接口:指通过这个接口的信息和它相关的定时信号是以同一方向传输的。

G703接口是数字网络接口建议。随着光纤通信和数字传输技术的飞速发展,利用64Kbit/s和2Mbit/s速率的数字信道传输数据的应用越来越多,G.703建议定义了分级数字接口的物理/电气特性。数字接口的比特率分级由G.702建议规定。

专用方式需为继电保护敷设专用的光纤通道。复用方式利用64kbit/s的数字接口经PCM终端设备或利用2M接口直接接入现有数字用户网络系统,不需再敷设光缆,同时传输距离也大大提高,可延伸到数字用户网络的每一个通信接点。

kb/s同反相板最多提供4路同反相接口,通过网管软件可以设置为同向或反相接口。指示灯说明: RUN :运行指示,绿灯。当G703板工作正常时该灯闪亮。 ALM :告警指示,红灯。当G703板时钟或同步丢失时,红灯亮。

ISDN基群速率接口也称一次群速率接口,即30B+D,B和D均为64kbit/s的数字信道。B信道主要用于传送用户信息流;D信道主要用于传送电路交换的信令信息。

到此,以上就是小编对于信号跨时钟域处理的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏