本篇目录:

- 1、pcb设计中FPGA与高速并行DAC的布线应该注意什么?

- 2、fpga的serdes是什么

- 3、为什么CPU主频比FPGA快那么多,但是却说FPGA可以加速

- 4、为什么要用fpga来实现千兆以太网传输速率

- 5、我现在需要用STM32控制FPGA并且和FPGA进行通讯,请问STM32和FPGA的接口...

- 6、FPGA与电脑串口通信verilog程序

pcb设计中FPGA与高速并行DAC的布线应该注意什么?

高速D/A,时钟信号频率一般很高,布线时应让时钟信号传输线尽量短,必要时可以采用屏蔽线传输,以降低时钟干扰。DDS集成芯片,性能优于FPGA内设计的频率合成单元。

高速信号PCB布线应注意什么?电源滤波一定要做好,否则有纹波。正电源(VCC)的所有线路最好用两根地线(GND)将它夹在中间,(如果整个板子都铺铜,这个可以不考虑)。

注:具体PCB的层的设置时,要对以上原则进行灵活掌握,在领会以上原则的基础上,根据实际单板的需求,如:是否需要一关键布线层、电源、地平面的分割情况等,确定层的排布,切忌生搬硬套,或抠住一点不放。

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。

电路设计要注意的十四个误区 误区一:这板子的PCB 设计要求不高,就用细一点的线,自动布吧。

fpga的serdes是什么

SERDES是序列化/解序列化器的简称,是一种实现高速、多协议通信的芯片设计技术,用于将并行数据转换为串行数据及将串行数据转换为并行数据。

SerDes硬核作为高端FPGA的冲击市场的有力武器,而对于低端FPGA来说,软的SerDes不失为一种非常好的研究方向。每个月。根据查询招聘软件得知,serdes高速接口设计薪酬为40000元每个月。

SerDes是英文SERializer(串行器)/DESerializer(解串器)的简称。

为什么CPU主频比FPGA快那么多,但是却说FPGA可以加速

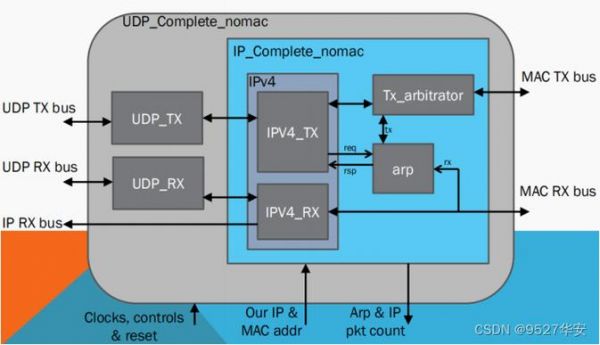

CPU和GPU都属于冯·诺依曼结构,指令译码执行,共享内存。FPGA之所以比CPU、GPU更快,本质上是因为其无指令,无共享内存的体系结构所决定的。

FPGA的计算速度快是源于它本质上是无指令、无需共享内存的体系结构。对于保存状态的需求,FPGA中的寄存器和片上内存(BRAM)是属于各自的控制逻辑的,无需不必要的仲裁和缓存,因此FPGA在运算速度足够快,优于GPU。

通过与目标硬件的高速接口互联,FPGA可以完成目标硬件运行效率比较低的部分,从而在系统层面实现加速。现如今通用处理器(CPU)的摩尔定律已入暮年,而机器学习和Web服务的规模却在指数级增长。

为什么要用fpga来实现千兆以太网传输速率

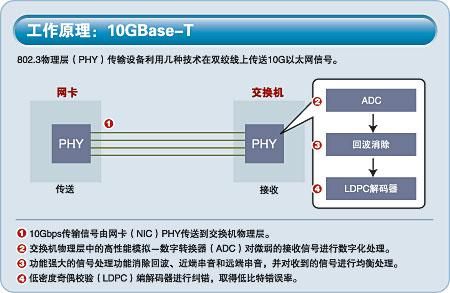

写了用以太网传输的优点,相对于串口的传输速度慢,并且不能远距离传输。PCIE不能远距离传输,选择以太网兼顾了传输速率和系统使用灵活的特点。

FPGA作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计。

我对FPGA的了解还只是皮毛,以前也只做过FPGA+STM32以太网传输的项目,当时用FPGA只是因为它的速度快,其实这个和CPLD+单片机是相同的。你上面说了,它们三者单独都有这些能力,当然,这是在低速场合才成立。

千兆以太网可以保护公司在以太网和快速以太网的设施上已有的投资;第三,它能够提供一种简单、有效而又廉价的性能提升办法,同时又能继续使用大量现有的水平线缆传输介质。

对比国产星载计算机在以太网方面的现状,分析表明,该系统通用性更好,数据处理性能更高,数据传输速率最高可达1 Gb/s。

.千兆位以太网提供完美无缺的迁移途径,充分保护在现有网络基础设施上的投资。

我现在需要用STM32控制FPGA并且和FPGA进行通讯,请问STM32和FPGA的接口...

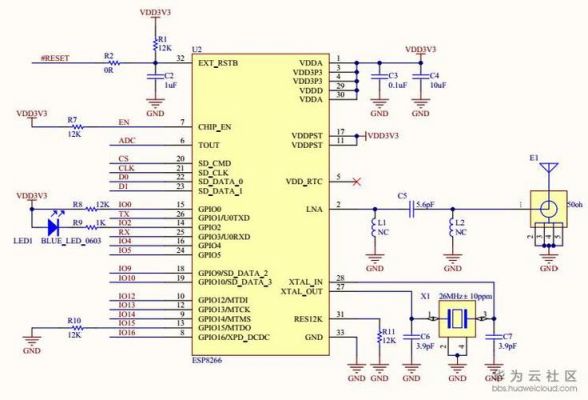

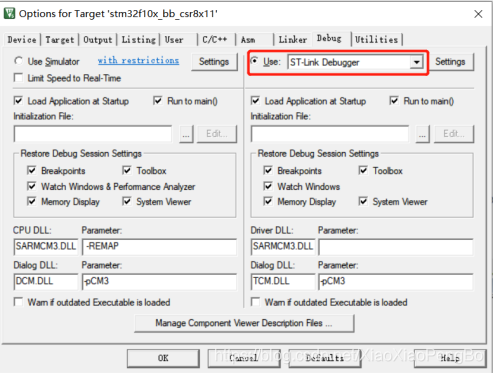

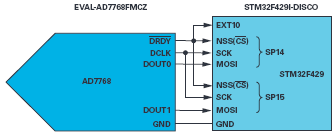

选用STM32为配置处理器,存储单元用SPI FLASH M25P64, 64Mbits/8MB,比我目前看上的XC6SLX150容量还要大接近1倍。

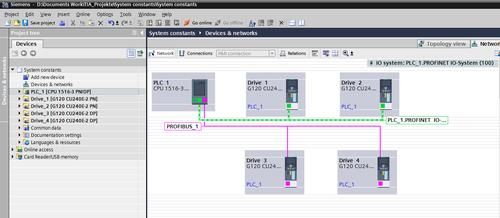

如果用并行接口的话,STM32用FSMC与FPGA通信,优点是速度快,缺点是之间相连的线多。如果用并行接口的话,可以用UART、或者SPI也很方便,连线少,对通信速度要求不高的应用完全可以胜任。

stm32正常按读写SDRAM进行配置,FPGA进行信号采集。FPGA信号采集发现SDWNE是高但H7手册上时序显示是低,造成无法像FPGA模拟的SDRAM无法写入数据 FPGA采集信号应该在时钟下降沿,上升沿采集,数据会发生错误。

FPGA与电脑串口通信verilog程序

小灯亮灭的时间掌握好,用一个计数器来掌握小灯亮灭的时间,不一定要分频。比如说,50MHz的时钟,小灯没1秒变化一次,那么1秒钟走过了50M个时钟,所以把计数器的最大值设置为50M。每次计数器益处,小灯的状态变化。

FPGA的JTGA没有什么设置就可以下进去的,但是AS有三个引脚设置的,如果下载不进去,首先看AS那几个引脚电路是否正确,然后就是看设置是否正确。再就是看你是否生成了相应的AS下载文件。

inout [8:0] data = read_en ? data_read : 8bz;只要让数据总线在读有效的时候等于你模块内部的由地址线决定的要读出的数据,其他时间保持高阻态即可。至于写数据,直接取data值就行了。

本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在PC机上安装一个串口调试工具来验证程序的功能。

这一步其实在综合之前不是最后完成的时候进行的)。

到此,以上就是小编对于高速串行传输协议有哪些的问题就介绍到这了,希望介绍的几点解答对大家有用,有任何问题和不懂的,欢迎各位老师在评论区讨论,给我留言。

微信扫一扫打赏

微信扫一扫打赏